Università degli Studi di Ferrara

# DOTTORATO DI RICERCA IN MATEMATICA-INFORMATICA

COORDINATORE PROF.SSA LUISA ZANGHIRATI

# JANUS: A RECONFIGURABLE SYSTEM FOR SCIENTIFIC COMPUTING

**DOTTORANDO** DOTT. FILIPPO MANTOVANI **TUTORE** PROF. RAFFAELE TRIPICCIONE

XXI° CICLO

ANNI 2006 - 2008

A Manuela

# Contents

| In       | Introduction 1 |        |                                                              |                |  |  |  |  |

|----------|----------------|--------|--------------------------------------------------------------|----------------|--|--|--|--|

| 1        | Intr           | oducti | ion to reconfigurable computing                              | 5              |  |  |  |  |

|          | 1.1            | Gener  | al purpose architectures                                     | 6              |  |  |  |  |

|          | 1.2            | Doma   | in-specific architectures                                    | $\overline{7}$ |  |  |  |  |

|          | 1.3            | Applie | cation-specific architectures                                | 8              |  |  |  |  |

|          | 1.4            | Progra | ammable logic, FPGA                                          | 9              |  |  |  |  |

|          | 1.5            | Recon  | figurable Computing                                          | 11             |  |  |  |  |

|          |                | 1.5.1  | Pervasiveness of RC                                          | 13             |  |  |  |  |

|          |                | 1.5.2  | The Hartenstein's point of view                              | 13             |  |  |  |  |

|          |                | 1.5.3  | Man does not live by hardware only                           | 14             |  |  |  |  |

|          | 1.6            | Non e  | xhaustive history of RC                                      | 15             |  |  |  |  |

|          |                | 1.6.1  | Common features                                              | 16             |  |  |  |  |

|          |                | 1.6.2  | Fix-plus machine (Estrin)                                    | 17             |  |  |  |  |

|          |                | 1.6.3  | Rammig Machine                                               | 17             |  |  |  |  |

|          |                | 1.6.4  | Xputer (Hartenstein)                                         | 18             |  |  |  |  |

|          |                | 1.6.5  | PAM, VCC and Splash                                          | 19             |  |  |  |  |

|          |                | 1.6.6  | Cray XD1                                                     | 21             |  |  |  |  |

|          |                | 1.6.7  | RAMP (Bee2)                                                  | 21             |  |  |  |  |

|          |                | 1.6.8  | FAST (DRC)                                                   | 22             |  |  |  |  |

|          |                | 1.6.9  | High-Performance Reconfigurable Computing: Maxwell and Janus | 23             |  |  |  |  |

| <b>2</b> | Mo             | nte Ca | rlo methods for statistical physics                          | 29             |  |  |  |  |

|          | 2.1            |        |                                                              | 29             |  |  |  |  |

|          |                | 2.1.1  | •                                                            | 33             |  |  |  |  |

|          |                | 2.1.2  | -                                                            | 35             |  |  |  |  |

|          |                | 2.1.3  |                                                              | 36             |  |  |  |  |

|          | 2.2            |        |                                                              | 38             |  |  |  |  |

|          |                | 2.2.1  |                                                              | 38             |  |  |  |  |

|          |                | 2.2.2  | -                                                            | 39             |  |  |  |  |

|   |                                | 2.2.3   | Metropolis algorithm                                                                                                    | ļ |  |  |  |  |  |  |

|---|--------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

|   |                                | 2.2.4   | How to use the Metropolis algorithm for spin systems 42                                                                 | ) |  |  |  |  |  |  |

|   |                                | 2.2.5   | Another MC algorithm: the heat bath                                                                                     | j |  |  |  |  |  |  |

|   |                                | 2.2.6   | Parallel tempering techniques                                                                                           | 2 |  |  |  |  |  |  |

|   | 2.3                            | Nume    | rical requirements                                                                                                      | ) |  |  |  |  |  |  |

|   |                                | 2.3.1   | Implementation and available parallelism                                                                                | j |  |  |  |  |  |  |

|   |                                | 2.3.2   | Techniques on a general purpose processor                                                                               | , |  |  |  |  |  |  |

|   |                                | 2.3.3   | Random numbers                                                                                                          | I |  |  |  |  |  |  |

| 3 | Janus architecture at large 5' |         |                                                                                                                         |   |  |  |  |  |  |  |

|   | 3.1                            | Janus   | project                                                                                                                 | ļ |  |  |  |  |  |  |

|   | 3.2                            | Questi  | ions leading Janus's development                                                                                        | J |  |  |  |  |  |  |

|   |                                | 3.2.1   | Why many nodes on a board?                                                                                              | ļ |  |  |  |  |  |  |

|   |                                | 3.2.2   | Why an Input/Output processor?                                                                                          | J |  |  |  |  |  |  |

|   |                                | 3.2.3   | How are organized communications between Janus boards and                                                               |   |  |  |  |  |  |  |

|   |                                |         | Janus host?                                                                                                             | - |  |  |  |  |  |  |

|   |                                | 3.2.4   | How are organized communications within a Janus board? 64                                                               | 2 |  |  |  |  |  |  |

|   |                                | 3.2.5   | Why a nearest neighbours network?                                                                                       | j |  |  |  |  |  |  |

|   |                                | 3.2.6   | Why do boards have no direct link among them self? 67                                                                   | , |  |  |  |  |  |  |

|   |                                | 3.2.7   | Why only 17 nodes per board? 68                                                                                         | ļ |  |  |  |  |  |  |

|   |                                | 3.2.8   | Why do the nodes have no off chip memory?                                                                               | į |  |  |  |  |  |  |

|   |                                | 3.2.9   | Which clock frequency and why? 69                                                                                       | I |  |  |  |  |  |  |

|   | 3.3                            | SP firm | mware: spin glass                                                                                                       | I |  |  |  |  |  |  |

|   |                                | 3.3.1   | Parallelism                                                                                                             | I |  |  |  |  |  |  |

|   |                                | 3.3.2   | Algorithm Implementation                                                                                                | - |  |  |  |  |  |  |

|   | 3.4                            | SP firm | mware: parallel tempering                                                                                               | 2 |  |  |  |  |  |  |

|   | 3.5                            | SP firm | mware: graph coloring                                                                                                   | , |  |  |  |  |  |  |

|   |                                | 3.5.1   | Memory organization                                                                                                     | , |  |  |  |  |  |  |

|   |                                | 3.5.2   | Janus limitations in graph coloring                                                                                     | I |  |  |  |  |  |  |

| 4 | Arc                            | hitectı | ral details of Janus 85                                                                                                 | , |  |  |  |  |  |  |

|   | 4.1                            | FPGA    | .: different flavours                                                                                                   | ) |  |  |  |  |  |  |

|   | 4.2                            | Struct  | ure of a Janus board                                                                                                    | , |  |  |  |  |  |  |

|   |                                | 4.2.1   | SP                                                                                                                      | , |  |  |  |  |  |  |

|   |                                | 4.2.2   | IOP                                                                                                                     | J |  |  |  |  |  |  |

|   |                                | 4.2.3   | PB                                                                                                                      | - |  |  |  |  |  |  |

|   |                                | 4.2.4   | Janus box                                                                                                               | 2 |  |  |  |  |  |  |

|   | 4.3                            | The I   | $OP in depth \ldots $ | ļ |  |  |  |  |  |  |

|   |                                | 4.3.1   | Clock handling: topClock                                                                                                | 2 |  |  |  |  |  |  |

|   |                                | 4.3.2   | Double data rate: iddrBus and oddrBus                                                                                   | , |  |  |  |  |  |  |

|              |                    | 4.3.3 Message routing: StreamRouter                                                                                                                                          |  |  |  |  |  |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|              |                    | 4.3.4 Memory controller: memExt                                                                                                                                              |  |  |  |  |  |

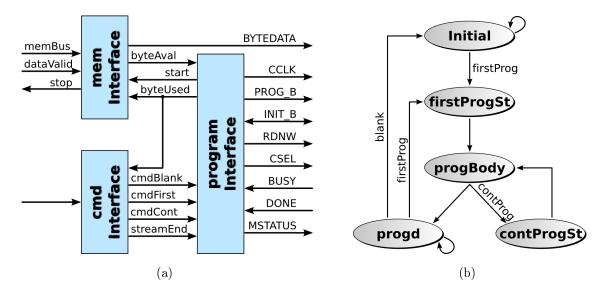

|              |                    | 4.3.5 SP reconfiguration interface: mainProgInt                                                                                                                              |  |  |  |  |  |

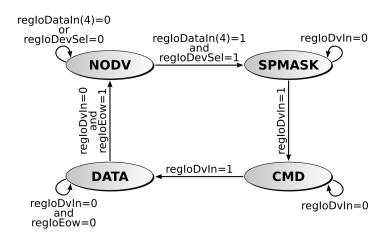

|              |                    | 4.3.6 SP communication: spInt                                                                                                                                                |  |  |  |  |  |

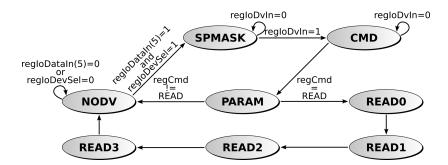

|              |                    | 4.3.7 Synchronization device: syncInt $\ldots \ldots \ldots$ |  |  |  |  |  |

|              | 4.4                | SP firmwares for Janus test                                                                                                                                                  |  |  |  |  |  |

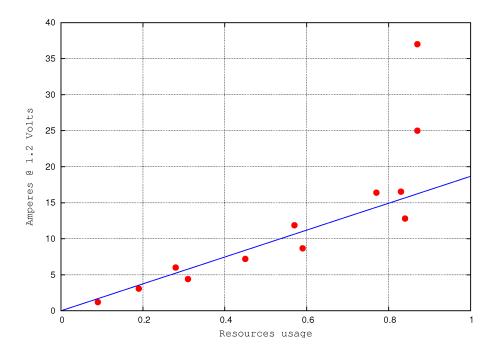

|              | 4.5                | Engineering problems                                                                                                                                                         |  |  |  |  |  |

| <b>5</b>     | Per                | formance and results 111                                                                                                                                                     |  |  |  |  |  |

|              | 5.1                | Useful concepts                                                                                                                                                              |  |  |  |  |  |

|              |                    | 5.1.1 About the equilibrium                                                                                                                                                  |  |  |  |  |  |

|              |                    | 5.1.2 Correlation $\ldots \ldots \ldots$                     |  |  |  |  |  |

|              |                    | 5.1.3 Order parameters: magnetization and overlap                                                                                                                            |  |  |  |  |  |

|              | 5.2                | First run details                                                                                                                                                            |  |  |  |  |  |

|              | 5.3                | Janus performance                                                                                                                                                            |  |  |  |  |  |

|              | 5.4                | Physics results overview                                                                                                                                                     |  |  |  |  |  |

|              |                    | 5.4.1 Non-equilibrium dynamics of a large EA spin glass 119                                                                                                                  |  |  |  |  |  |

|              |                    | 5.4.2 The 4-state Potts model and its phase structure                                                                                                                        |  |  |  |  |  |

| Co           | onclu              | sions 129                                                                                                                                                                    |  |  |  |  |  |

| $\mathbf{A}$ | Not                | es on the IOP communication strategy 133                                                                                                                                     |  |  |  |  |  |

|              | A.1                | Overview of the IOP structure                                                                                                                                                |  |  |  |  |  |

|              | A.2                | First idea: the stuff byte                                                                                                                                                   |  |  |  |  |  |

|              |                    | A.2.1 Which stuff-value?                                                                                                                                                     |  |  |  |  |  |

|              |                    | A.2.2 Performance problem                                                                                                                                                    |  |  |  |  |  |

|              | A.3                | Second idea: the tagged stream                                                                                                                                               |  |  |  |  |  |

|              |                    | A.3.1 Remarks                                                                                                                                                                |  |  |  |  |  |

|              | A.4                | Third idea: the encapsulated stream                                                                                                                                          |  |  |  |  |  |

|              |                    | A.4.1 Pros and cons                                                                                                                                                          |  |  |  |  |  |

| Ri           | Ringraziamenti 139 |                                                                                                                                                                              |  |  |  |  |  |

# Introduction

The widespread diffusion of field programmable gate arrays (FPGA) and their remarkable technological developments have allowed reconfigurable computing to play an increasingly important role in computer architectures. This trend should be very evident in the field of high performance, as the possibility to have a huge number of gates that can be configured as needed opens the way to new approaches for computationally very intensive tasks.

Even if the reconfigurable approach has several advantages, its impact so far has been limited. There are several reasons that may explain why reconfigurable computing is still in a corner:

- i) the costs in terms of time and the specific technical skills needed to develop an application using programmable logic is by far higher than those associated to programming an application in an appropriate programming language, even considering a reasonable amount of (possibly platform-specific) optimization for performance;

- ii) strictly correlated with the point above, software tools performing a (more or less) automatic and transparent transitions from a conventional computer approach to a reconfigurable computing structure are still in an embryonic phase and in a too fragmentary stage of development;

- iii) the interface between reconfigurable devices and standard processors is often not standard and therefore almost any project developing a system housing an FPGA side by side to a conventional architecture defines a new data-exchange protocol, so even the simplest communication primitives cannot be standardized. While this lack of standardization does provide opportunities for those willing (and able to) consider innovative designs, it is only perceived as a further obstacle for any attempt to provide a standard development environment for reconfigurable systems.

In spite of these drawbacks, there are several areas of computational sciences where the reconfigurable approach is able to provide such a large performance boost as to provide adequate compensation to the disadvantages described above. Hardware resources of recent FPGA generations allow us to map complex algorithms directly within just one device, configuring the available gates in order to perform a computationally heavy tasks with high efficiency. In some cases, moreover, these applications have computing requirements that are large enough to justify even huge development efforts.

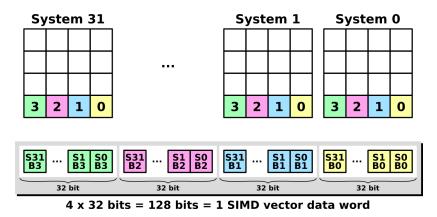

A paradigmatic example of this situation is the study of a particular class of theoretical physics models called *spin glasses* performed using Monte Carlo methods. The algorithms relevant in this field are characterized by *i*. large intrinsic parallelism that allows one to implement a trivial SIMD approach (i.e. many Monte Carlo update engines within a single FPGA); *ii*. relatively small size of the computational data base (~2 MByte), that can be fully stored into on-chip memories; *iii*. large use of good quality random numbers (up to 1024 per clock cycle); *iv*. integer arithmetic and simple logic operations. Careful tailoring of the architecture to the specific features of the algorithms listed above makes it possible to reach impressive performance levels: just one FPGA has the same performance as ~ 1000 standard PC with a recent state-of-the-art processor (this will be explained in details in chapter 5).

The Janus project was started approximately 3 years ago in order to harvest all the potential advantages offered by reconfigurable computing for spin-glass simulations. Janus is a collaboration among the Spanish Universities of Zaragoza, Madrid and Extremadura, the BIFI Institute of Zaragoza and the Italian Universities of Ferrara and Roma I with the industrial partnership of the Eurotech Group. The main aim of the project is to build an FPGA based supercomputer strongly oriented to study and solve the computational problems associated to the simulation of the spin systems introduced above.

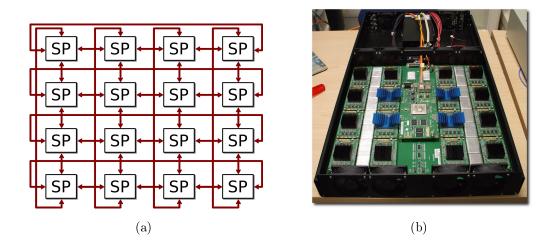

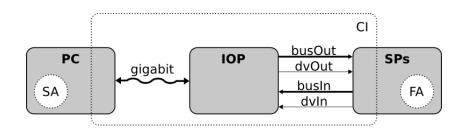

Janus is a system composed of three logical layers. The hardware layer includes several (16 in the first system, deployed in December 2007) boards each housing 17 FPGA-based subsystem: 16 so-called scientific processors (SPs) and one input/output processor (IOP). A standard PC (called the Janus host) connects to up to two Janus boards and controls their functionalities via the IOP module.

At the software layer we find the communication libraries, developed in order to allow the user to interface his applications with Janus, and the physics libraries, a set of routines written in C that simplifies the operations of setting up of a lattice spin simulation on Janus. By we also developing these libraries, in some sense we define an interface between our FPGA-based system and a general purpose processorbased computer. We obviously need such an interface to operate our machine, but we concede that in this way we give our fair contribution to increasing the entropy of reconfigurable computing interfaces (on the other hand, since we deal with statistical physics, we know very well that decreasing entropy is a more formidable tasks than writing a PhD thesis).

The third layer is composed of the firmware for the FPGAs running the simulation codes, that is the set of parametric SP firmware that implements different spin models and the IOP-based firmware that includes several IO interfaces, a memory controller, a configuration controller driving the configuration of the SPs and several debug interfaces. All these firmware modules are handcrafted in VHDL. No automatic translation tools from high level languages to hardware description languages has been used, since we consider optimization of the usage of logic resources and computational performance as our primary goal.

The Janus project started in 2004 with preliminary meetings between Italian researchers and the Spanish group that built in the '80s another FPGA based machine, called *Spin Update Engine* (SUE). During my laurea degree I studied spin models and implemented a Monte Carlo simulation engine on an FPGA: this initial experiment, that we named *SuperSUE*, assessed the viability and the expected performances of a smassively parallel system based on latest generation FPGAs based.

In summer 2006 the Eurotech group assembled the first three prototype Janus boards, using Xilinx Virtex-4 LX160 FPGAs. One year later, the first Janus rack, powered by 256 Xilinx Virtex-4 LX200 based computational nodes was tested. Acceptance tests on this large system ended before Christmas 2007 and in march 2008 we performed the first large scale run (a simulation stretching uninterruptedly for over 25 days with just one system crash of a couple of hour due to severe weather conditions that caused a power failure). The results of this run were reported in our application for the 2008 Gordon Bell Prize. Unfortunately, at least one Gordon Bell referee made the argument that only floating point performance is relevant for that award.

The Janus installation in Zaragoza was officially unveiled in June 2008, and, since then, has been always in operation, running several physics codes.

I was involved in all the phases of the project. In details during my first two PhD years I was involved at the hardware layer of the project, developing the overall hardware design of the system, working on the detailed structure of all its subsystems and developing procedures for hardware tests. This period was characterized by a strong interaction with engineers of the Eurotech group, the company that actually built our hardware. Another relevant work of this period was the development of the firmware for the IOP and some firmwares modules for the SPs, that we needed to test all implemented hardware functionalities. The final period of my PhD studies was dedicated to realize a complete test bench in order to validate the system as it was assembled.

I also worked on some preliminary studies for the Janus implementation of an efficient firmware for random graph coloring.

This thesis has 5 chapters, structured as follows:

In Chapter 1 I review basic concepts of reconfigurable computing and I include a non exhaustive history of the projects that marked developments in this area.

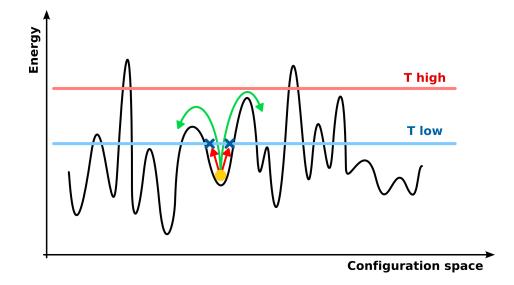

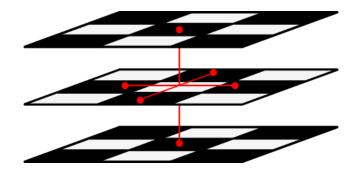

Chapter 2 is an introduction to the physics concepts and simulation algorithms for which Janus has been designed and built. I introduce the Edward-Anderson spin model, the graph coloring problem and the Monte Carlo algorithms used to investigate them (Metropolis, Heat Bath and Parallel Tempering).

Chapter 3 is dedicated to a general discussion of the Janus architecture. I briefly describe hardware components and then I discuss a set of important architectural questions that I handled during the development of Janus prototypes.

In Chapter 4 I highlight selected significant details about the Janus basic hardware elements, about the IOP and SP firmware and a brief description of the test environment developed to check the Janus boards.

Chapter 5 is a short review of the most important physics results obtained so far with Janus, including a detailed analysis of performances.

My work is wrapped up in the concluding chapter.

When you got nothing, you got nothing to lose.

Bob Dylan

# 1

# Introduction to reconfigurable computing

Research in the architecture of computer systems has always played a central role in the computer science and high performance computing communities. The investigation goals vary according to the target applications, the price of the final equipment, the programmability and the scalability of the system and many others.

Until a few years ago for processors to be used in parallel machines for high-performance computing the focus was placed on high clock rates, parallelism of different chips and high communication bandwidth at the expense of power. Recently, however, attention has focused on multi core and many core architectures with the aim of taking advantage of the presence on-chip of more than one complex calculation unit, adding to the historical problem of the needs of bandwidth between chips the new challenge of a careful handling of parallelism among cores within a single chip.

On the other hand in the embedded systems environment the governing factor during development is in many cases the price of the final equipment and the main aim is to use optimized components in order to contain costs and optimize power consumption. A small microcontroller is used, for instance, to control data acquisition from sensors and provide data to a collector system at a very low frequency. In those systems the architectures are focused on containing power consumption and costs and are in some cases carefully tailored for specific areas.

A third example in which the architecture plays a key role is the environment in which some specific duties should be executed extremely efficiently depending on a small set of constraints. An example could be a rover used to explore a given area: its architecture will be carefully tailored to the specific application of image collection, elaboration and transmission and, at the same time, to obstacle detection.

We consider the three examples given above as illustrating of the big scenario of the architectures that can be analyzed by splitting it in three main groups:

- general purpose architectures based on the Von Neumann computing paradigm;

- *domain-specific architectures* designed for class of applications having common features;

- application-specific architectures developed for only one specific application;

## **1.1** General purpose architectures

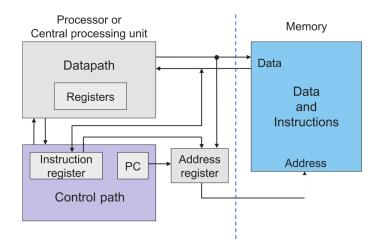

In 1945, the mathematician John Von Neumann demonstrated in a study of computation [1] that is possible to have a simple fixed architecture able to execute any kind of computation, given a properly programmed control, without the need for hardware modification. The Von Neumann contribution was universally adopted and quickly became the groundwork of future generations of high-speed digital computers. One of the reasons for the acceptance of the Von Neumann approach is its simplicity of programming that follows the sequential way of human thinking. The general structure of a Von Neumann machine as shown in Figure 1.1 consists of:

- A memory for storing program and data. Harvard architectures contain two parallel accessible memories for storing program and data separately.

- A control unit (also called control path) featuring a program counter that holds the address of the next instruction to be executed.

- An arithmetic and logic unit (also called data path) in which instructions are executed.

A program is coded as a set of instructions to be executed sequentially, instruction after instruction. At each step of the program execution, the next instruction is fetched from the memory at the address specified in the program counter and decoded. The required operands are then collected from the memory before the instruction is executed. After execution, the result is written back into the memory. In this process, the control path is in charge of setting all signals necessary to read from and write to the memory, and to allow the data path to perform the right computation. The data path is controlled by the control path, which interprets the instructions and sets the control signals accordingly to execute the desired operation.

In general, the execution of an instruction on a Von Neumann computer can be done in five cycles: Instruction Read (IR) in which an instruction is fetched from the

Figure 1.1 – A scheme of the Von Neumann computer architecture (source [2]).

memory; Decoding (D) in which the meaning of the instruction is determined and the operands are localized; Read Operands (R) in which the operands are read from the memory; Execute (EX) in which the instruction is executed with the read operands; Write Result (W) in which the result of the execution is stored back to the memory. In each of those five cycles, only the part of the hardware involved in the computation is activated. The rest remains idle. For example if the IR cycle is to be performed, the program counter will be activated to get the address of the instruction, the memory will be addressed and the instruction register to store the instruction before decoding will be also activated. Apart from those three units (program counter, memory and instruction register), all the other units remain idle.

Decades of research in computer architectures developed techniques to optimize the organization of processors as the ones described above. The extraction of the instruction level parallelism, the so called *pipelining*, the multiple issue architectures, the branch prediction or the optimized instruction scheduling are only a few examples of the breakthroughs in this subject. For an exhaustive overview of architectural optimizations see [3].

### 1.2 Domain-specific architectures

A domain-specific processor is a processor tailored for a class of algorithms. As mentioned in the previous section, the data path is tailored for an optimal execution of a common set of operations that mostly characterizes the algorithms in the given class. Also, memory access is reduced as much as possible. Digital Signal Processor (DSP) are among the most used domain-specific processors.

A DSP is a specialized processor used to speed-up computation of repetitive, numerically intensive tasks in signal processing areas such as telecommunication, multimedia, automobile, radar, sonar, seismic, image processing, etc. The most often cited feature of DSPs is their ability to perform one or more multiply accumulate (MAC) operations in single cycle. Usually, MAC operations have to be performed on a huge set of data. In a MAC operation, data are first multiplied and then added to an accumulated value. The normal Von Neumann computer would perform a MAC in 10 steps. The first instruction (multiply) would be fetched, then decoded, then the operand would be read and multiply, the result would be stored back and the next instruction (accumulate) would be read, the result stored in the previous step would be read again and added to the accumulated value and the result would be stored back. DSPs avoid those steps by using specialized hardware that directly performs the addition after multiplication without having to access the memory.

Because many DSP algorithms involve performing repetitive computations, most DSP processors provide special support for efficient looping. Often a special loop or repeat instruction is provided, which allows a loop implementation without expending any instruction cycles for updating and testing the loop counter or branching back to the top of the loop. DSPs are also customized for data with a given width according to the application domain. For example if a DSP is to be used for image processing, then pixels have to be processed. If the pixels are represented in Red Green Blue (RGB) system where each colour is represented by a byte, then an image processing DSP will not need more than 8 bit data path. Obviously, the image processing DSP cannot be used again for applications requiring 32 bits computation.

This specialization of DSP's functions increases the performance of the processor and improves device utilization, but reduces the execution efficiency of an arbitrary application.

#### **1.3** Application-specific architectures

Although DSPs incorporate a degree of application-specific features such as MAC and data width optimization, they still hide the Von Neumann approach and, therefore, remain sequential machines. Their performance is limited. If a processor has to be used for only one application, which is known and fixed in advance, then the processing unit could be designed and optimized for that particular application. In this case, we say that the hardware "fits" itself to the application. This kind of approach is useful, for instance, when a processor has to perform tasks defined by a standard, such as encoding and decoding of an audio/video stream.

A processor designed for only one application is called an Application-Specific Processor (ASIP). In an ASIP, the instruction cycles (IR, D, R, EX, W) are eliminated: there is no fetch of instructions because the instruction set of the application is directly implemented in hardware, or, in other words the algorithm to perform is hardwired in a custom processor. Therefore a data stream works as input, the processor performs the required computation and the results can be collected at the outputs of the processor.

ASIPs use a spatial approach to implement only one application. The gates building the final processor are configured so that they constitute all the functional units needed for the computation of all parts of the application. This kind of computation is called *spatial computing* [4]. Once again, an ASIP that is built to perform a given computation cannot be used for other tasks other than those for which it has been originally designed.

ASIPs are usually implemented as single chips called *Application-Specific Integrated Circuit*, ASIC, or using devices housing programmable logic. This approach arose in the late '80's with the widespread commercial availability of reconfigurable chips called *Field Programmable Gate Arrays*, FPGAs.

## 1.4 Programmable logic, FPGA

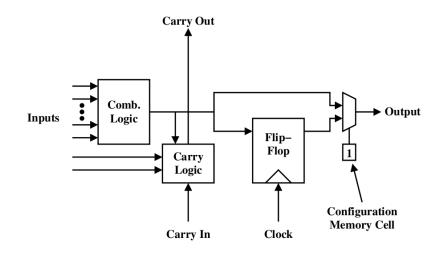

The FPGA is a regularly tiled two-dimensional array of logic blocks. Each logic block includes a Look-Up Table (LUT), a simple memory that can store an arbitrary *n*-input boolean function. The logic blocks communicate through a programmable interconnection network that includes both nearest neighbor as well as hierarchical and long path wires. The periphery of the FPGA contains I/O blocks to interface between the internal logic blocks and the I/O pins. This simple, homogeneous architecture has evolved to become much more heterogeneous, including on-chip memory blocks as well as DSP blocks such as multiply/multiply-accumulate units.

There are several sorts of FPGAs, including those that can be programmed only once, but the application-specific architectures may require that the device can be reconfigured on-the-fly during a run or between separate runs to obtains different behaviours. Depending on the needs of the applications it is possible to use devices basing their reconfiguration on SRAM (faster) or FLASH (slower) but this is only a technological detail. In both cases this means that the configuration of the FPGA, the *object code* defining the algorithm loaded onto the device, is stored in an on-chip storage device. By loading different configurations into this configuration device, different algorithms can be executed. The configuration determines the boolean function computed by each logic block and the interconnection pattern between logic and I/O blocks.

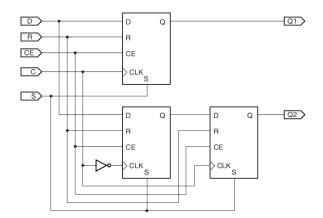

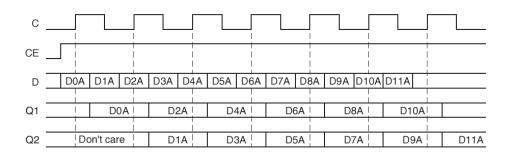

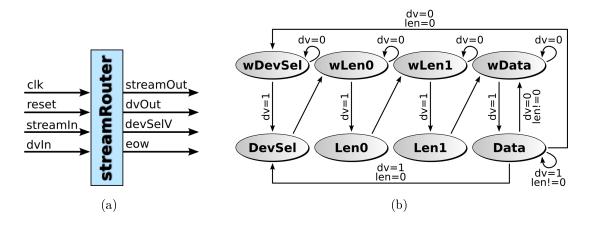

FPGA designers have developed a large variety of programmable logic structures for FPGAs since their invention in the mid-1980's. For more than a decade, much of the programmable logic used in FPGAs can be generalized as shown in Figure 1.2. The basic logic element generally contains some form of programmable combinational logic, a flip-flop or latch, and some fast carry logic to reduce the area and delay costs

Figure 1.2 – A generic programmable logic block (source [5]).

for implementing carry logic. In our generic logic block, the output of the block is selectable between the output of the combinational logic or the output of the flip-flop. The figure also illustrates that some form of programming, or configuration, memory is used to control the output multiplexer; of course, configuration memory is used throughout the logic block to control the specific function of each element within the block.

In addition to the relatively *fine-grained* configurability provided by FPGAs and similar devices, the drive to reduce the power, area, and/or delay costs of fine-grained reconfigurability has led to a number of what may be called *coarse-grained* reconfigurable logic devices. Instead of providing configurability at the level of individual gates, flip-flops or look-up tables (LUTs), these coarse-grained architectures often provide arithmetic logic units (ALUs) and other larger functions that can be combined to perform computations. In the extreme, the functions might be as large as microprocessor cores such as in the Raw chip from MIT [6].

With their introduction in 1985, FPGAs have been an alternative for implementing digital logic in systems. The earlier use of the FPGAs were to provide a denser solution for glue logic within systems, but now they have expanded their applications to the point that it is common to find FPGAs as the central processing devices within systems. The reason of their increased diffusion and use lies mainly in the available resources embedded within a single chip: most of the FPGA family of the main brand offers in fact today not only logic resources, but also embedded memories, DSP block, high speed IO pins, hardwired IP core for the interface with PCI or other standard communication protocol. Compared with application-specific integrated circuits (ASICs), FPGAs have several advantages for their users, including: quick time to market, being a standard product; no non-recurring engineering costs for fabrication; pre-tested silicon for use by the designer; and reprogrammability, allowing designers to upgrade or change logic through in-system programming. By reconfiguring the device with a new circuit, design errors can be fixed, new features can be added, or the function of the hardware can be entirely retargeted to other applications. Of course, compared with ASICs, FPGAs cost more per chip to perform a particular function so they are not good for extremely high volumes. Also, an FPGA implementation of a function is slower than the fixed-silicon options.

## 1.5 Reconfigurable Computing

From the discussion in sections 1.1 1.2 1.3, where we introduced three different kinds of processing units, we can identify two main means to characterize processors: flexibility and performance.

The computers based on Von Neumann paradigm are very flexible because they are in principle able to compute any kind of task: therefore we refer to them with the terminology general purpose processors. Although there are many kind of optimizing procedures and tricks their general purpose orientation has a cost in terms of performance: for instance, the five steps (IR, D, R, EX, W) needed to perform one instruction becomes a major drawback, in particular if the same instruction has to be executed on huge sets of data; moreover their intrinsic sequential structure is useful for the programmer because it is similar to the human thought process but is a natural hindrance for a possible parallel computing approach for some applications. With this architecture we have thus a high level of *flexibility* because the hardware structure is fixed and, in many cases, is hidden to the programmer by the compiler that play the role to "fit" the application in the hardware in order to be executed. We could use the catchphrase: with general purpose processors the application must always fits in the hardware.

On the other side the application-specific architectures bring high performance because they are optimized for a particular application. The instruction set required for that application can then be built in a chip, but we pay a high cost in terms of flexibility. In this case the important goals are the performance of the processor and the hardware is shaped by the application. From this is possible we can invent the opposite catchphrase: in presence of application-specific architectures the hardware always fits in the application.

Between these two extreme positions, general purpose processors and applicationspecific processors, there is, architecturally speaking, an interesting *space* in which we find different types of processors. We can classify them depending on their performance and their flexibility.

If we consider, after this analysis, the features of the FPGAs introduced briefly in section 1.4 we can easily see that they allow us to implement hardware architectures that merge the flexibility of a general purpose processor and the performance of an application-specific processor with the comfort of the reconfigurability. In other words, the boost that FPGA technology gives to researchers studying the architectures a powerful tool to try to efficiently fill the space between general purpose and application-specific processors. We consider therefore FPGAs as the way to build a reconfigurable hardware or reconfigurable device or *Reconfigurable Processing Unit*, RPU, in analogy with the Central Processing Unit, CPU. Following this, the study of computation using reconfigurable devices is commonly called *Reconfigurable Computing*.

For a given application, at a given time, the spatial structure of the device will be modified such as to use the best computing approach to speed up that application. If a new application has to be computed, the device structure will be modified again to match the new application. Contrary to the Von Neumann computers, which are programmed by a set of instructions to be executed sequentially, the structure of reconfigurable devices are changed by modifying all or part of the hardware at compiletime or at run-time, usually by downloading a so called bitstream into the device. In this sense we call *configuration* or *reconfiguration* the process of changing the structure of a reconfigurable device respectively at star-up-time or at run-time.

Other than this difference of approach the major operative differences between reconfigurable and processor-based computing are:

- The FPGA is configured into a customized hardware implementation of the application. The hardware is usually data path driven, with minimal control flow; processor-based computing depends on a linear instruction stream including loops and branches.

- The reconfigurable computer data path is usually pipelined so that all function units are in use every clock cycle. The microprocessor has the potential for multiple instructions per clock cycle, but the delivered parallelism depends on the instruction mix of the specific program, and function units are often underutilized.

- The reconfigurable computer can access many memory words in each clock cycle, and the memory addresses and access patterns can be optimized for the application. The processor reads data through the data cache, and efficiency of the processor is determined by the degree to which data is available in the cache when needed by an instruction. The programmer only indirectly controls the cache-friendliness of the algorithm, as access to the data cache is hidden from the instruction set architecture.

- The FPGA has in principle no constraints about the size of data words: the words of the data path can have arbitrary length. Using the general purpose architectures the length of the data words is fixed and the programmer has no fine control on it.

To summarize, reconfigurable computing is concerned with decomposing applications into spatially parallel, tiled, application-specific pipelines, whereas the traditional general purpose processor interprets a linear sequence of instruction, with pipelining and other forms of spatial parallelism hidden within the microarchitecture of the processor.

Progress in reconfiguration has been amazing in the last two decades. This is mostly due to the wide acceptance of the Field Programmable Gate Array (FPGAs) that are now established as the most widely used reconfigurable devices.

#### 1.5.1 Pervasiveness of RC

There are two main fields in which the reconfigurable computing has been mostly accepted, developed and used: embedded computing and scientific computing.

There are *social reasons* for that analyzed in [7]: people with expertise developing embedded systems have hardware background and see in FPGAs a cheap solution to develop custom systems with the possibility to fix with new firmware releases their projects so that the development and the update of an FPGA-based system is easier and faster than with other components. Also this category of people with hardware background is in many cases familiar with hardware description languages and with hardware implementation techniques and can obtain impressive boost of performance with a relative low prices and power consumption.

From scientific computing come problems often with very special requirements and in many cases it is possible to implement their algorithms directly within an FPGA. Depending on the project the FPGAs can be configured as the co-processor of a general purpose processor or a main-custom processor. A limiting factor for to this kind of project comes often from the absence of a specific hardware background of the people involved: in some cases in fact the need to develop a design using hardware description languages can require a long development period and a drastic change of the paradigm of programming. Because of this some groups and companies develop and sell tools for the *translation* of standard codes, like C, for instance, to various hardware description language. These automatic tools of translation can speed up and make easier the development process, but sometimes have big limitations on the code structures that can be translated and the extraction of parallelism may not always be efficient.

#### 1.5.2 The Hartenstein's point of view

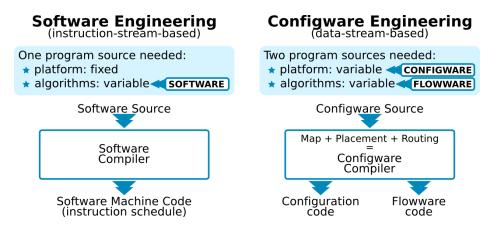

The most common architectural approach in computer science is the Von Neumann paradigm and the most used processors are based on the general purpose architectures. The reconfigurable computing approach requires a deep change of programming paradigm in comparison with the Von Neumann: R. Hartenstein starting from 1990 gave a formalisation of it in [8, 9, 10]. Theoretically speaking, there is in the RC environment a different view of the software and the hardware. In the Von Neumann approach the hardware resources are fixed, only one source code is needed and the compiler processing it generates an instruction-stream to be stored in the program memory waiting the scheduled time to be executed.

The RC approach requires two different type of source code, *configware* and *flowware*. Configware is commonly written using some abstraction of an hardware description language and is synthesised using a tool that translates the code describing the custom architecture into logic gates, maps it on the FPGA resources and produces as output a so called bitstream, a configuration file to properly set up the FPGA resources. Flowware is code written with a high level programming language generating a stream of data used as input for the custom architecture implemented within the FPGA. As sometimes the platform housing the reconfigurable device is not a "standard" mother board with "standard" communication protocols, the flowware implements also communication interfaces and other features useful for the system. Reconfigurable systems require moreover that configuration/reconfiguration of the logic is performed external to the device: in some cases a PROM is used to set up the reconfigurable device on boot, but it is useful to have the possibility to reconfigure the devices "on the fly". This require that flowware is able to perform this task too. Figure 1.3 summarize the theoretical schemes of two approach: Von Neumann and reconfigurable computing.

**Figure 1.3** – On the left the organization of Software Engineering in the classic Von Neumann point of view; on the right a schema of the Configure Engineering theorized by Hartenstein (adapted from [7]).

#### 1.5.3 Man does not live by hardware only

On the theoretical side Hartenstein tries to formalize the principles of reconfigurable computing. Following this idea and thanks to the increasing resources offered by the FPGAs many people built therefore systems based on programmable logic and many of these projects developed interfaces to connect general purpose architecture and FPGA based systems [11, 12, 13, 14] trying to define a standard interface in order to:

- access reconfigurable hardware resources without introducing undesirable dependencies on hardware;

- avoid client code changes whenever the hardware is revised;

- leave the programmer free to know or ignore the hardware details of interfaces or low level protocols;

- develop a set of libraries optimized for scientific computing and reprogrammable logic based coprocessors [12].

All these efforts are focused on solving a basic problem coming from reconfigurable computing and formalized by Hartenstein: which is the way to efficiently use the huge degrees of freedom coming from the FPGA while maintaining programmability accessible to a large part of the computer science community?

A first approach to solve it is to completely ignore the programmability and the generalization of the design in order to obtain the best performances from the logics: this approach is commonly adopted by groups or projects developing efficient applicationspecific architectures that are not interested in developing a general purpose machine, but only a performance oriented custom machine.

The second opposite approach comes from groups and projects studying systems oriented to a large enough set of applications and in which the availability of as friendly a programming environment as possible can justify a considerable loss of performance.

#### **1.6** Non exhaustive history of RC

Like most technologies, reconfigurable computing systems are built on a variety of existing technologies and techniques. It is always difficult to pinpoint the exact moment a new area of technology comes into existence or even to pinpoint which is the first system in a new class of machines. Popular scientific history often gives simple accounts of individuals and projects that represent a turning point for a particular technology, but in reality the story is usually more complicated.

The large number of exotic high-performance systems designed and built over a very short time makes this area particularly difficult to document, but there is also a problem specific to them. Much of the work was done inside various government agencies, particularly in the United States, and was never published. In these cases, all that can be relied on is currently available records and publications.

#### **1.6.1** Common features

Reconfigurable systems are distinguished from other cellular multiprocessor systems. Array processors, in particular Single Instruction Multiple Data Processors (SIMD), are considered architecturally distinct from reconfigurable machines, in spite of many similarities. This distinction arises primarily from the programming techniques. Array processors tend to have either a shared or dedicated instruction sequencer and take standard instruction-style programming code. Reconfigurable machines tend to be programmed spatially, with different physical regions of the device being configured at different times. This necessarily means that they will be slower to reprogram than cellular multiprocessor systems but should be more flexible and achieve higher performance for a given silicon area.

Although FPGA-based systems are very different each others, it is possible to extract some shared features concerning both architectures of systems housing reconfigurable devices and architecture of designs within the FPGAs.

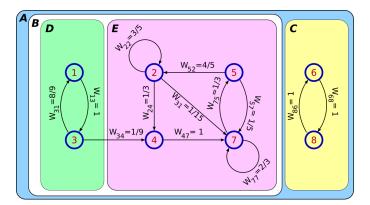

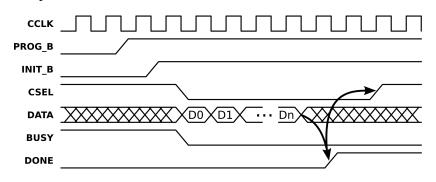

The systems using FPGA are in many cases configured as master-slave systems: a general purpose architecture works as master, runs the flowware and handles communications with the slave system with one or more reconfigurable devices. In general slave systems are custom boards housing in addition to one or more FPGAs other components like for instance external memory, communications devices, special I/O devices etc. Although the structure of the system housing reconfigurable logics could change among different projects, the global scheme of a system involved FPGAs can be summarize in general as show in Figure 1.4.

**Figure 1.4** – A generic reconfigurable system is composed by a **Slave System** housing a programmable device (FPGA) and a **Master System** allowing the (re-)configuration of the programmable device and handling the communications with it.

As said before, reconfigurable devices are programmed spatially, thus different regions have different tasks and each region can be programmed (configured) in different times. Despite this large degree of freedom, some constraints coming from the chip vendors are fixed for the developer: position of the I/O blocks, distribution of internal memories, clock drivers and clock trees are common problems for a developer using FPGA. Moreover, even if a programmer finds the infrastructure already built, a fixed structure is forced by the design of the system housing the FPGA so that some areas of the chip are reserved for logic blocks performing specific task, as for instance I/O interfaces or memory controllers. A common feature of all reconfigurable computing projects is therefore the presence of some kind of spatial constraints.

#### 1.6.2 Fix-plus machine (Estrin)

In 1959, Gerald Estrin, a computer scientist of the university of California at Los Angeles, introduced the concept of reconfigurable computing. The following fragment of an Estrin publication in 1960 [15] on the fix-plus machine, defines the concept of reconfigurable computing paradigm.

"Pragmatic problem studies predicts gains in computation speeds in a variety of computational tasks when executed on appropriate problemoriented configurations of the variable structure computer. The economic feasibility of the system is based on utilization of essentially the same hardware in a variety of special purpose structures. This capability is achieved by programmed or physical restructuring of a part of the hardware."

To implement this vision, Estrin designed a computing system, the fix-plus machine, that like many reconfigurable computing systems available today, was composed of a fixed architecture (a proto-general purpose processor) and a variable part consisting of logic operators that could be manually changed in order to execute different operations.

#### 1.6.3 Rammig Machine

In the year 1977, Franz J. Rammig, a researcher at the university of Dortmund proposed a concept for editing hardware [16]. The goal was:

"investigation of a system, which, with no manual or mechanical interference, permits the building, changing, processing and destruction of real (not simulated) digital hardware."

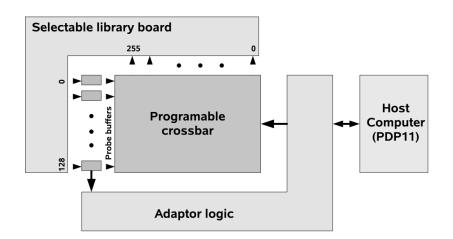

Rammig realised his concept by developing a hardware editor similar to today's FPGA architecture. The editor was build upon a set of modules, a set of pins and a one-to-one mapping function on the set of pins. The circuitry of a given function was then defined as a *string* on an alphabet of two letters (w = wired and u = unwired). To build the hardware editor, *selectors* were provided with the modules' outputs connected to the input of the selectors and the output of the selectors connected to the input of the modules. The overall system architecture is shown in Figure 1.5.

The implementation of the *{wired, unwired}* property was done through a programmable crossbar switch, made upon an array of selectors. The bit strings were provided by storing the selector control in registers, and by making these registers accessible from a host computer, the PDP11 in those days. The modules were provided

Figure 1.5 – Structure of the Rammig Machine (source [2]).

on a library board similar to that of Estrin's Fix-Plus. Each board could be selected under software control. The mapping from module I/Os to pins was realized manually, by a wiring of the provided library boards, i.e. fixed per library board.

#### 1.6.4 Xputer (Hartenstein)

The Xputer's concept was presented in early 1980s by Reiner Hartenstein, a researcher at the University of Kaiserslautern in Germany [8].

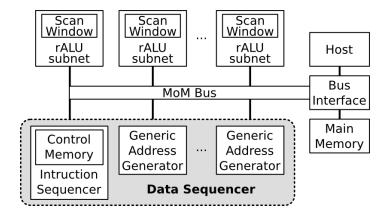

The goal was to have a very high degree of programmable parallelism in the hardware, at the lowest possible level, to obtain performance not possible with the Von Neumann computers. Instead of sequencing the instructions, the Xputer would sequence data, thus exploiting the regularity in the data dependencies of some class of applications like image processing, where repetitive processing is performed on a large amount of data. An Xputer consists of three main parts: the data sequencer, the data memory and the *reconfigurable ALU*, rALU, that permits the run-time configuration of communication at levels below instruction set level. Within a loop, data to be processed were accessed via a data structure called the *scan window*. Data manipulation was done by the rALU that had access to many scan windows. The most essential part of the data sequencer was the *generic address generator*, GAG, that was able to produce address sequences corresponding to the data of up to three nested loops. An rALU subnet that could be configured to perform all computations on the data of a scan window was required for each level of a nested loop.

The general XPuter architecture is presented in Figure 1.6. This shows the realization of the XPuter as a *map oriented machine*, MoM [17]. The overall system was made upon a host processor, whose memory was accessible by the MoM. The rALU subnets received their data directly from local memory or from the host main memory via the MoM bus. Communication was also possible among the rALUs via direct serial

**Figure 1.6** – General architecture of the XPuter as implemented in the Map oriented Machine (MOM-3) prototype.

connections. Several XPuters could also be connected to provide more performance.

For executing a program, the hardware had to be configured first. If no reconfiguration took place at run-time, then only the data memory would be necessary. Otherwise, a configuration memory would be required to hold all the configurations to be used at run-time.

The basic building block of the reconfigurable ALU was the so-called *reconfigurable datapath unit*, rDPU. Several rDPUs were used within an rALU for data manipulation. Each rDPU had two registered inputs and two registered outputs with a data width of 32 bit. Input data were provided either from the north or from the west, while the south and east were used for the output. Besides the interconnection lines for the rALUs, a global I/O-Bus is available for the connection of designs to the external world. The I/O bus was principally used for accessing the scan windows.

The control implemented a program that is loaded on reconfiguration to control different units of the rALU. Its instruction set consisted of instructions for loading the data as well as instructions for collecting results from the field. Application of the XPuters was in image processing, systolic array and signal processing.

#### 1.6.5 PAM, VCC and Splash

In the late 1980s, PAM, VCC, and Splash, three significant general-purpose systems using multiple FPGAs, were designed and built. They were similar in that they used multiple FPGAs, communicated to a host computer across a standard system bus, and were aimed squarely at reconfigurable computing.

The *Programmable Active Memories*, PAM, project [18] at Digital Equipment Corporation (DEC) initially used four Xilinx XC3000-series FPGAs. The original Perle-0 board contained 25 Xilinx XC3090 devices in a  $5 \times 5$  array, attached to which were four independent banks of fast static RAM (SRAM), arranged as  $64K \times 64$  bits, which were

controlled by an additional two XC3090 FPGA devices. This wide and fast memory provided the FPGA array with high bandwidth. The Perle-0 was quickly upgraded to the more recent XC4000 series. As the size of the available XC4000-series devices grew, the PAM family used a smaller array of FPGA devices, eventually settling on  $2 \times 2$ . Based at the DEC research lab, the PAM project ran for over a decade and continued in spite of the acquisition of DEC by Compaq and then the later acquisition of Compaq by Hewlett-Packard. PAM, in its various versions, plugged into the standard PCI bus in a PC or workstation and was marked by a relatively large number of interesting applications as well as some groundbreaking work in software tools. It was made available commercially and became a popular research platform.

The Virtual Computer from the Virtual Computer Corporation, VCC, [19] was perhaps the first commercially available reconfigurable computing platform. Its original version was an array of Xilinx XC4010 devices and I-Cube programmable interconnect devices in a checkerboard pattern, with the I-Cube devices essentially serving as a crossbar switch. The topology of the interconnection for these large FPGA arrays was an important issue at this time: With a logic density of approximately 10K gates and input/output (I/O) pins on the order of 200, a major concern was communication across FPGAs. The I-Cube devices were perceived as providing more flexibility, although each switch had to be programmed, which increased the design complexity. The first Virtual Computer used an  $8 \times 8$  array of alternating FPGA and I-Cube devices. The exception was on the left and right sides of the array, which exclusively used FPGAs, which consumed 40 Xilinx XC4010 FPGAs and 24 I-Cubes. Along the left and right sides were 16 banks of independent  $16 \times 8K$  dual-ported SRAM, and attached to the top row were 4 more banks of standard single-ported  $256K \times 32$  bits SRAM controlled by an additional 12 Xilinx XC4010 FPGAs. While this system was large and relatively expensive, and had limited software support, VCC went on to offer several families of reconfigurable systems over the next decade and a half.

The Splash system [20, 21], from the Supercomputer Research Center (SRC) at the Institute for Defense Analysis, was perhaps the largest and most heavily used of these early systems. Splash was a linear array consisting of XC3000-series Xilinx devices interfacing to a host system via a PCI bus. Multiple boards could be hosted in a single system, and multiple systems could be connected together. Although the Splash system was primarily built and used by the Department of Defense, a large amount of information on it was made available. A Splash 2 [22] system quickly followed and was made commercially available from Annapolis Microsystems. The Splash 2 board consisted of two rows of eight Xilinx XC4010 devices, each with a small local memory. These 16 FPGA/memory pairs were connected to a crossbar switch, with another dedicated FPGA/memory pair used as a controller for the rest of the system. Much of the work using Splash concentrated on defense applications such as cryptography and pattern matching, but the associated tools effort was also notable, particularly some of the earliest high-level language (HLL) to hardware description language (HDL) translation software targeting reconfigurable machines. Specifically, the data parallel C compiler and its debug tools and libraries provided reconfigurable systems with a new level of software support.

PAM, VCC, and Splash represent the early large-scale reconfigurable computing systems that emerged in the late 1980s. They each had a relatively long lifetime and were upgraded with new FPGAs as denser versions became available. Also of interest is the origin of each system. One was primarily a military effort (Splash), another emerged from a corporate research lab (PAM), and the third was from a small commercial company (Virtual Computer). It was this sort of widespread appeal that was to characterize the rapid expansion of reconfigurable computing systems during the 1990s.

#### 1.6.6 Cray XD1

While the number of small reconfigurable coprocessing boards would continue to proliferate as commercial FPGA devices became denser and cheaper, other new hardware architectures were produced to address the needs of large-scale supercomputer users. Unlike the earlier generation of boards and systems that sought to put as much reconfigurable logic as possible into a single unified system, these machines took a different approach. In general, they were traditional multiprocessor systems, but each processing node in them consisted of a very powerful commercial desktop microprocessor combined with a large commercial FPGA device. Another factor that made these systems unique is that they were all offered by mainstream commercial vendors.

The first reconfigurable supercomputing machine from Cray, the XD1 [23], is based on a chassis of 12 processing nodes, with each node consisting of an AMD Opteron processor. Up to 6 reconfigurable computing processing nodes, based on the Xilinx Virtex-2 Pro devices, can also be configured in each chassis, and up to 12 chassis can be combined in a single cabinet, with multiple cabinets making larger systems. Hundreds of processing nodes can be easily configured with this approach.

#### 1.6.7 RAMP (Bee2)

Around 2005 the choice of the computer hardware industry to focus production on single-chip multiprocessors gave a boost to the idea of developing a system able to simulate highly parallel architectures at hardware speeds. The *Research Accelerator* for Multiple Processors, RAMP, is the open-source FPGA-based project that arose from this idea [24, 25]: its main aim is to develop and share the hardware and software necessary to create parallel architectures.

The computational support of RAMP project is the system BEE2 [26] using Xilinx Virtex-2 Pro FPGAs as primary and only processing elements. A peculiarity of this system is the PowerPC 405 embedded on the FPGA that makes it possible to minimize latency between microprocessor and reconfigurable logic while maximizing the data throughput. Moreover the BEE2 system is an example of an FPGA-based system that does not require explicitly a master system checking over the tasks of the reconfigurable logic: each FPGA embeds in fact general purpose processors able to control itself.

Each BEE2 compute module consists of five Xilinx Virtex-2 Pro-70 FPGA chips, each directly connected and logically organized into four compute FPGAs and one control FPGA. The control FPGA has additional global interconnect interfaces and control signals to the secondary system components, while the compute modules are connected as a  $2 \times 2$  mesh.

The architecture of the BEE2 leaves some degrees of freedom and using the 4X Infiniband physical connections, the compute modules can be wired into many network topologies, such as a 3D mesh. For applications requiring high-bisection-bandwidth random communication among many compute modules, the BEE2 system is designed to take advantage of commercial network switch technology, such as Infiniband or 10G Ethernet. The compute module runs the Linux OS on the control FPGA with a full IP network stack. Moreover each BEE2 system is equipped with high bandwidth memories (DDR, DDR2) and other I/O interfaces.

As well as being a hardware architecture project, RAMP aims to support the software community as it struggles to take advantage of the potential capabilities of parallel microprocessors, by providing a malleable platform through which the software community can collaborate with the hardware community.

#### 1.6.8 FAST (DRC)

FPGA-Accelerated Simulation Technologies (FAST) [27], is a today's project developed by the University of Texas at Austin that attempts to speed up the simulation of complex computer architectures. It gives a methodology to build extremely fast, cycle-accurate full system simulators that run real applications on top of real operating systems. Current state of the project allows one to boot unmodified Windows XP, Linux 2.4 and Linux 2.6 and run unmodified applications on top of those operating systems at simulation speeds in the 1.2 MIPS range, between 100 and 1000 times faster than Intel's and AMD's cycle-accurate simulators (e.g. which is fast enough to type into Microsoft Word). I knew people of this project during my visit at the University of Texas in summer 2008.

The hardware platform used to develop this project is a DRC development system (DS2002). This machine contains a dual-socket motherboard, where one socket contains an AMD Opteron 275 (2.2GHz) and the other socket contains a Xilinx Virtex-4

LX200 (4VLX200) FPGA. The Opteron communicates to the FPGA via HyperTransport. The functional model runs on the Opteron and the timing model runs on the FPGA. DRC provides libraries to read and write from the FPGA. Interesting feature regarding the hardware platform is the fact that an FPGA uses a standard socket of a general purpose processor and not custom interfaces.

## 1.6.9 High-Performance Reconfigurable Computing: Maxwell and Janus

The high-performance computing field is traditionally dominated by clusters of general purpose processors and a common approach of the scientists is to find a machine as fast as possible to run a given code, if possible with no changes of it. This approach do not require in principle an understanding of the architecture or the hardware features of the machine running the code. On the other hand it is known that code optimization with respect to architectural details improves the performance of applications.

Despite that there are studies about the viability of reconfigurable supercomputing [28] and some projects with relevant results in this field.

The FPGA High Performance Computing Alliance (FHPCA) [29] was established in 2004 and is dedicated to the use of Xilinx FPGAs to deliver new levels of computational performance for real-world industrial applications. Led by EPCC, the supercomputing centre at The University of Edinburgh, the FHPCA is funded by Scottish Enterprise and builds on the skills of Nallatech Ltd, Alpha Data Ltd, Xilinx Development Corporation, Algotronix and ISLI.

Maxwell [30, 31, 32] is a high-performance computer developed by the FHPCA to demonstrate the feasibility of running computationally demanding applications on an array of FPGAs. Not only can Maxwell demonstrate the numerical performance achievable from reconfigurable computing, but it also serves as a testbed for tools and techniques to port applications to such systems.

The unique architecture of Maxwell comprises 32 blades housed in an IBM Blade Center. Each blade comprises one 2.8 GHz Xeon with 1 Gbyte memory and 2 Xilinx Virtex-4 FPGAs each on a PCI-X subassembly developed by Alpha Data and Nallatech. Each FPGA has either 512 Mbytes or 1 Gbyte of private memory. Whilst the Xeon and FPGAs on a particular blade can communicate with each other over the PCI bus (typical transfer bandwidths in excess of 600 Mbytes/s), the principal communication infrastructure comprises a fast Ethernet network with a high-performance switch linking the Xeons together and RocketIO linking the FPGAs. Each FPGA has 4 RocketIO links enabling the 64 FPGAs to be connected together in an 8×8 toroidal mesh. The RocketIO has a bandwidth in excess of 2.5 Gbits/s per link.

Together these two principal interconnect subsystems enable the efficient imple-

mentation of parallel codes where there is a need both for intensive numerical processing and for fast data communication between the cooperating processing elements.

The Parallel Toolkit developed by EPCC supports the decomposition of a numerically intensive application into a set of cooperating modules running on the array of Xeons in much the same way that many applications can be decomposed to run on a cluster of PCs. Each module can then be further analysed to identify the numerical "hot spots" which are then implemented on the FPGAs taking advantage of the fast RocketIO linking the FPGAs for fast communications. The implementation of the numerically intensive parts of the applications is accomplished using a combination of tools such as DIME-C from Nallatech, Handel-C from Celoxica and VHDL available from several vendors including Xilinx.

Janus is a project among universities of Italy and Spain with the main goal to realize a FPGA-based parallel system optimized a specific class of statistical physics simulations. Janus is composed of 256 Xilinx Virtex-4 FPGA organized in sets of 16 each connected via raw-ethernet Gigabit channel to a standard PC.

Both these projects give to the computer science community an efficient proof that reconfigurable computing can be used in order to obtain high performance machines as with a general purpose environment, in the Maxwell case, as in a very special and application specific case, in the Janus case. I discuss in depth details of Janus in the next chapters.

# Bibliography

- J. von Neumann, First Draft of a Report on the EDVAC, http://www.zmms.tu-berlin.de/~modys/MRT1/2003-08-TheFirstDraft.pdf.

1.1

- [2] C. Bobda, Introduction to Reconfigurable Computing: Architectures, Algorithms and Applications, Springer (2007). 1.1, 1.5

- [3] J. L. Hennessy, D. A. Patterson, Computer Architecture. A quantitative Approach (Fourth Edition), published by Morgan Kaufmann (2007). 1.1

- [4] A. DeHon, J. Wawrzynek, Reconfigurable Computing: What, Why, and Implications for Design Automation, Proceedings of the 36th ACM/IEEE conference on Design automation, pp. 610 - 615 (1999). 1.3

- [5] M. Gokhale, P. S. Graham, Reconfigurable Computing: Accelerating Computation with Field-programmable Gate Arrays, Birkhäuser (2005). 1.2

- [6] E. Waingold et al., Baring it all to Software: The Raw Machine, Computer, vol. 30, n. 9, pp. 86-93 (1997). 1.4

- [7] R. Hartenstein, Why we need Reconfigurable Computing Education, Introduction, opening session of the first International Workshop on Reconfigurable Computing Education, Karlsruhe (2006). 1.5.1, 1.3

- [8] R. Hartenstein, A. Hirschbiel, and M.Weber, Xputers an open family of non Von Neumann architectures, in 11th ITG/GI Conference on Architektur von Rechensystemen, VDE-Verlag (1990). 1.5.2, 1.6.4

- [9] R. Hartenstein, Data-stream-based Computing: Models and Architectural Resources, Informacije Midem (Ljubljana), vol. 33, part 4, pp. 228-235 (2003). 1.5.2

- [10] R. Hartenstein, The von Neumann Syndrome, invited paper "Stamatis Vassiliadis Memorial Symposium", Delft, The Netherlands, (2007). 1.5.2

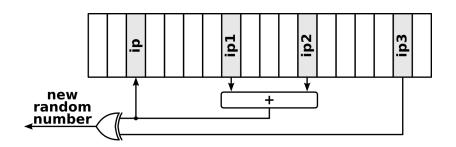

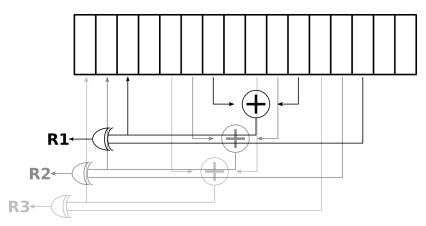

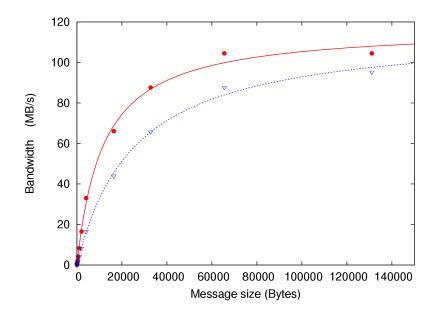

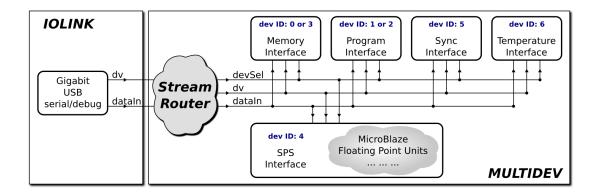

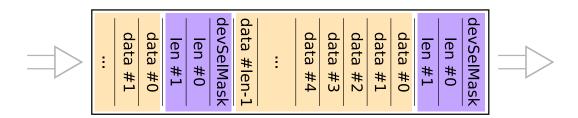

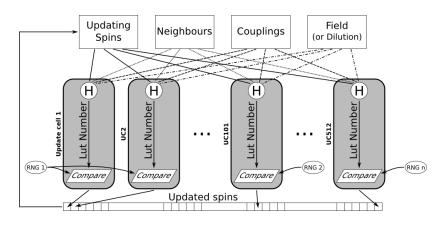

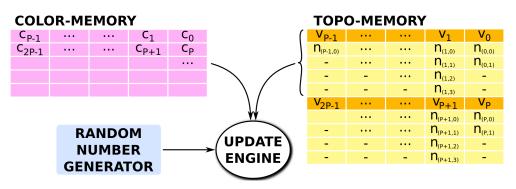

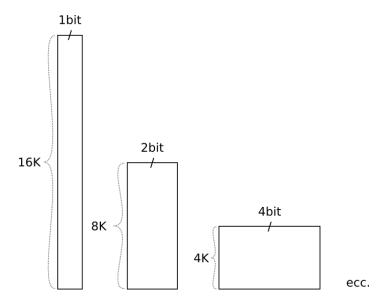

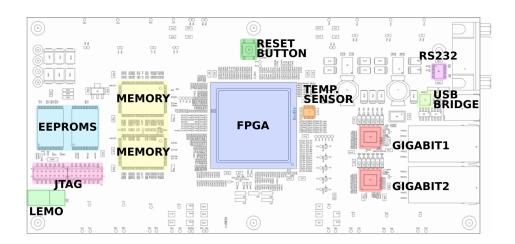

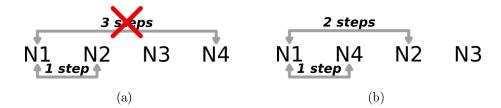

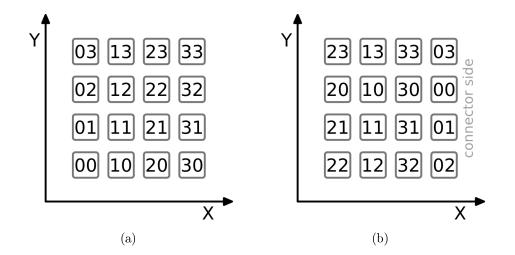

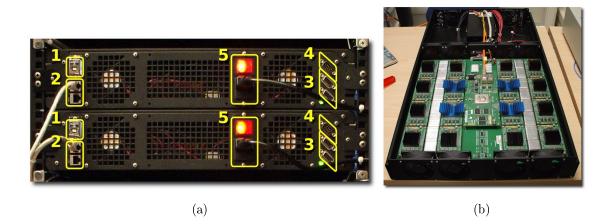

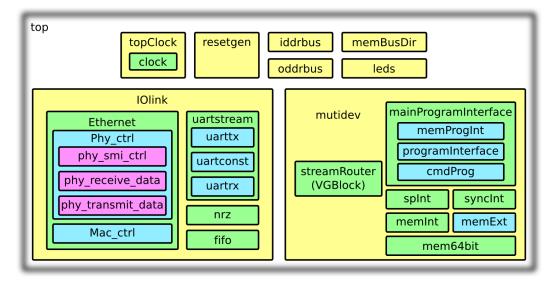

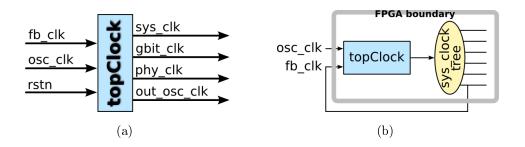

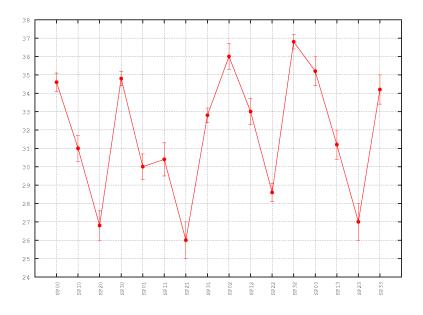

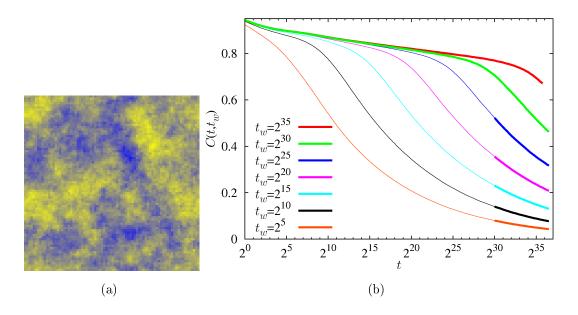

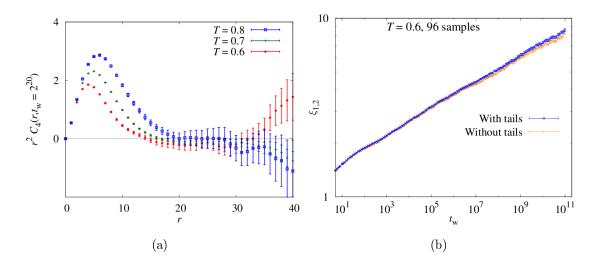

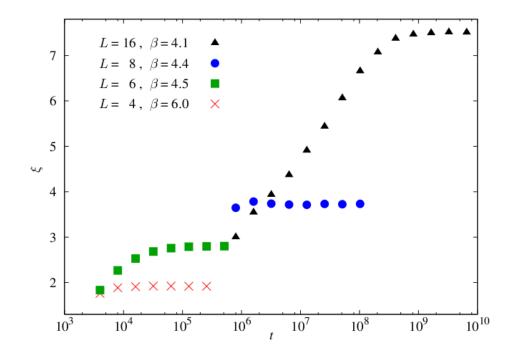

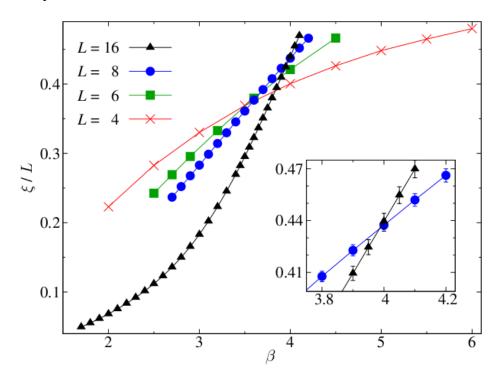

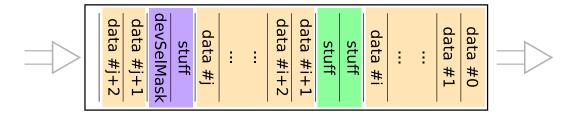

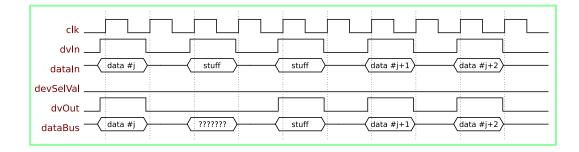

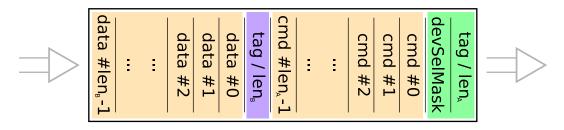

- [11] J. J. Koo et al., Evaluation of a high-level-language methodology for highperformance reconfigurable computers Proceedings of the IEEE 18th International Conference on Application-Specific Systems, Architectures and Processors (ASAP), pp. 30-35 (2007). 1.5.3