# DOTTORATO DI RICERCA IN "SCIENZE DELL'INGEGNERIA"

CICLO XXIV

COORDINATORE Prof. Stefano Trillo

# ELECTRICAL CHARACTERIZATION, PHYSICS, MODELING AND RELIABILITY OF INNOVATIVE NON-VOLATILE MEMORIES

Settore Scientifico Disciplinare ING/INF-01

| Dottorando              | Tutore            |

|-------------------------|-------------------|

| Dott. Zambelli Cristian | Prof. Olivo Piero |

| Lambelli Cristia        | ·eod_             |

|                         | (firma)           |

Anni 2009/2011

#### **Abstract**

Enclosed in this thesis work it can be found the results of a three years long research activity performed during the XXIV-th cycle of the Ph.D. school in Engineering Science of the Universitá degli Studi di Ferrara. The topic of this work is concerned about the electrical characterization, physics, modeling and reliability of innovative non-volatile memories, addressing most of the proposed alternative to the floating-gate based memories which currently are facing a technology dead end. Throughout the chapters of this thesis it will be provided a detailed characterization of the envisioned replacements for the common NOR and NAND Flash technologies into the near future embedded and MPSoCs (Multi Processing System on Chip) systems. In Chapter 1 it will be introduced the non-volatile memory technology with direct reference on nowadays Flash mainstream, providing indications and comments on why the system designers should be forced to change the approach to new memory concepts. In Chapter 2 it will be presented one of the most studied post-floating gate memory technology for MPSoCs: the Phase Change Memory. The results of an extensive electrical characterization performed on these devices led to important discoveries such as the kinematics of the erase operation and potential reliability threats in memory operations. A modeling framework has been developed to support the experimental results and to validate them on projected scaled technology. In Chapter 3 an embedded memory for automotive environment will be shown: the SimpleEE p-channel memory. The characterization of this memory proven the technology robustness providing at the same time new insights on the erratic bits phenomenon largely studied on NOR and NAND counterparts. Chapter 4 will show the research studies performed on a memory device based on the Nano-MEMS concept. This particular memory generation proves to be integrated in very harsh environment such as military applications, geothermal and space avionics. A detailed study on the physical principles underlying this memory will be presented. In Chapter 5 a successor of the standard NAND Flash will be analyzed: the Charge Trapping NAND. This kind of memory shares the same principles of the traditional floating gate technology except for the storage medium which now has been substituted by a discrete nature storage (i.e. silicon nitride traps). The conclusions and the results summary for each memory technology will be provided in Chapter 6. Finally, on Appendix A it will be shown the results of a recently started research activity on the high level reliability memory management exploiting the results of the studies for Phase Change Memories.

### **Abstract** (Italiano)

Racchiusi in questo lavoro di tesi si possono trovare i risultati della triennale attivitá di ricerca eseguita durante il XXIV-esimo ciclo del Dottorato di Ricerca in Scienze dell'Ingegneria svolto presso l'Universitá degli Studi di Ferrara. L'argomento di questa trattazione riguarda la caratterizzazione elettrica, la fisica, la modellistica e l'affidabilitá di memorie non-volatili innovative, indirizzando l'argomentazione verso le tecnologie proposte a rimpiazzare nel prossimo futuro le tradizionali memorie a gate flottante, ormai proiettate verso un naturale declino tecnologico. Attraverso i capitoli di questa tesi verrá fornita una caratterizzazione dettagliata dei possibili rimpiazzi delle NOR e NAND Flash nei prossimi sistemi embedded o a multi-processore. Nel Capitolo 1 verrá introdotta la tecnologia di memorie non-volatili con un chiaro riferimento alla tecnologia Flash, fornendo indicazioni e suggerimenti ad un ipotetico system designer verso il passaggio alla nuova generazione di memorie. Nel Capitolo 2 verrá presentata una delle memorie della post-floating gate generation più studiate nell'ultimo decennio: le memorie a cambiamento di fase (PCM). I risultati di una esaustiva caratterizzazione elettrica su questa tecnologia hanno permesso di scoprire fenomeni molto importanti quali la cinetica dell'operazione di cancellazione e altre potenziali minacce all'affidabilitá delle operazioni di scrittura sulle stesse. Un'intesa attivitá di modeling ha poi permesso di validare i risultati sperimentali in proiezione verso una tecnologia scalata. Nel Capitolo 3 verrá mostrata una memoria per ambiente automotive: la SimpleEE p-channel. La caratterizzazione elettrica di questa memoria ha permesso di provarne la robustezza e allo stesso tempo ha aiutato a capire meglio il fenomeno dei bit erratici giá presente nelle passate NOR e NAND. Il Capitolo 4 mostrerá gli studi eseguiti su una memoria basata su micro sistemi meccanici (Nano-MEMS) provandone la capacitá di integrazione in ambienti estremamente ostili per l'affidabilitá come sistemi militari, geotermici e avionica spaziale. Uno studio dettagliato sui principi fisici alla base di questa memoria verrá proposto. Il Capitolo 5 mostrerá il successore naturale della tecnologia Flash: le NAND Flash a intrappolamento di carica. Questo tipo di memorie usa gli stessi principi fisici delle memorie a floating gate per la memorizzazione dell'informazione, cambiando peró la natura del mezzo in cui i dati vengono immagazzinati (i.e. trappole di nitruro di silicio). Le conclusioni e il riassunto dei risultati sulle ricerche eseguite sulle varie tipologie di memoria verranno presentati nel Capitolo 6. In conclusione, nell'Appendice A verranno mostrati i risultati di un'attivitá di ricerca recentemente iniziata sulla gestione dell'affidabilitá delle memorie ad alto livello, sfruttando i risultati degli studi delle memorie a cambiamento di fase.

## **Contents**

| 1 | Intr | oduction                                            | 1  |

|---|------|-----------------------------------------------------|----|

|   | 1.1  | Intrinsic Flash reliability limits                  | 2  |

|   | 1.2  | Emerging issues of Flash technology                 | 10 |

| 2 | Pha  | se Change Memories                                  | 17 |

|   | 2.1  | Physics of chalcogenide-based memories              | 18 |

|   | 2.2  | Electrical characterization of PCM arrays           | 19 |

|   | 2.3  | Optimization of the writing operations              | 22 |

|   | 2.4  | Modeling the SET kinetics                           | 33 |

|   | 2.5  | The SET seasoning and the secondary shunt phenomena | 45 |

| 3 | P-ch | nannel SimpleEE Memories                            | 67 |

|   | 3.1  | Read performance                                    | 69 |

|   | 3.2  | Program/Erase speed                                 | 71 |

|   | 3.3  | Endurance and data retention                        | 73 |

|   | 3.4  | Disturbs robustness                                 | 76 |

|   | 3.5  | Evidence of the erratic bits                        | 79 |

| 4 | Nan  | oMEMS Memories                                      | 90 |

|          | •• |

|----------|----|

| CONTENTS | 11 |

| CONTENTS | 1. |

|          |    |

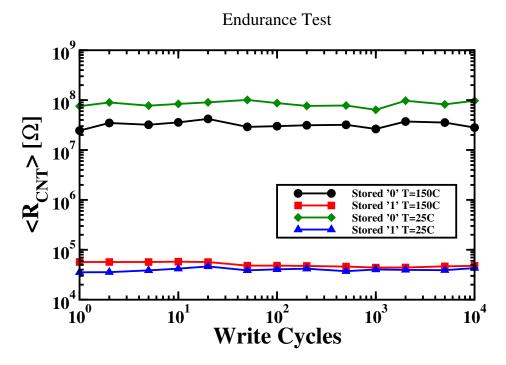

|   | 4.1  | Device physics                                | 91  |

|---|------|-----------------------------------------------|-----|

|   | 4.2  | Memory architecture                           | 95  |

|   | 4.3  | Endurance characterization                    | 97  |

|   | 4.4  | Data retention characterization               | 101 |

|   | 4.5  | Environmental and mechanical characterization | 103 |

| 5 | Cha  | rge Trapping NAND Flash Memories              | 106 |

|   | 5.1  | Electrical characterization                   | 107 |

|   | 5.2  | Program operation characterization            | 111 |

|   | 5.3  | Room temperature retention                    | 114 |

|   | 5.4  | Disturbs characterization                     | 116 |

|   | 5.5  | Edge Wordline Disturb (EWD) phenomenon        | 121 |

| 6 | Con  | clusions                                      | 138 |

| A | Syst | em-level reliability of non-volatile memories | 140 |

|   | A.1  | General idea                                  | 140 |

|   | A.2  | The physical view on PCM                      | 142 |

|   | A.3  | A case study                                  | 143 |

|   | A.4  | Experimental results                          | 146 |

|   |      |                                               |     |

## **List of Figures**

| 1.1 | FLOTOX device and its equivalent capacitance model                   | 3  |

|-----|----------------------------------------------------------------------|----|

| 1.2 | Band diagram sketch of tunneling effect                              | 4  |

| 1.3 | Band diagram during a program operation: without traps (solid        |    |

|     | lines in the oxide region) and with traps (dashed lines in the oxide |    |

|     | regions)                                                             | 7  |

| 1.4 | Threshold voltage degradation during cycling of NAND Flash           |    |

|     | with different geometrical features                                  | 7  |

| 1.5 | Band diagram of the cell when programmed and not biased. The         |    |

|     | main mechanism for data loss is tunneling through the tunnel oxide.  | 9  |

| 1.6 | Cumulative distribution of a NAND array on Program state. Both       |    |

|     | detrapping and SILC effects are appreciable on the time evolution.   | 10 |

| 1.7 | Two traps assisted tunneling (2TAT) band diagram (left) and com-     |    |

|     | parison between the SILC-2TAT model result versus the classical      |    |

|     | Fowler-Nordheim theory (right).                                      | 10 |

LIST OF FIGURES iv

| 1.8  | Condition for the depletion region near the gate-drain overlap re-   |    |

|------|----------------------------------------------------------------------|----|

|      | gion of a nMOS transistor when the surface is accumulated with       |    |

|      | a low negative gate bias (a), and n+ region is depleted or inverted  |    |

|      | with high negative gate bias (b)                                     | 13 |

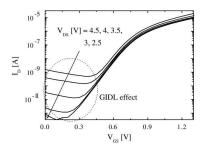

| 1.9  | Leakage current measured in a nMOS transistor for different          |    |

|      | Drain-Source voltages VDS in the subthreshold regime. When           |    |

|      | VGS approaches 0 V, for high VDS values the leakage current is       |    |

|      | due to GIDL                                                          | 13 |

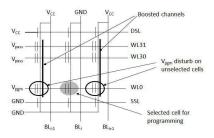

| 1.10 | Bias conditions possibly activating GIDL effects on SSL transis-     |    |

|      | tors belonging to columns $BL_{i-1}$ and $BL_{i+1}$                  | 14 |

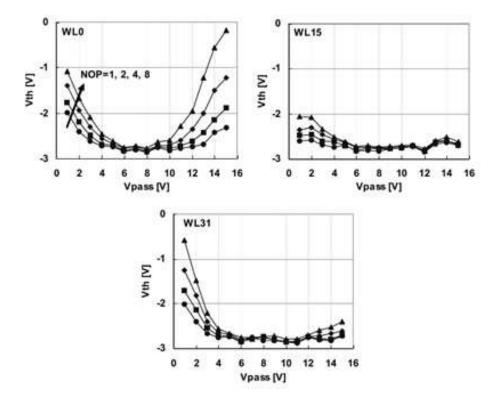

| 1.11 | Measured program disturbs characteristics for 3 cells belonging      |    |

|      | to WL0, WL15 and WL31, respectively. NOP indicates the num-          |    |

|      | ber of partial programming when multiple writing of a world line     |    |

|      | is allowed for specific applications. It can be observed that, for   |    |

|      | higher values of Vpass, the disturb on cell WL0 becomes signifi-     |    |

|      | cant                                                                 | 14 |

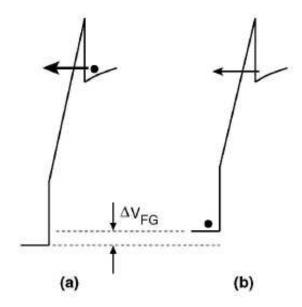

| 1.12 | Electrostatic effect on the injection process: the Floating Gate     |    |

|      | (FG) potential changes when an electron is injected from the sub-    |    |

|      | strate (a) to the FG (b), reducing the tunnel oxide field and the    |    |

|      | tunneling current                                                    | 16 |

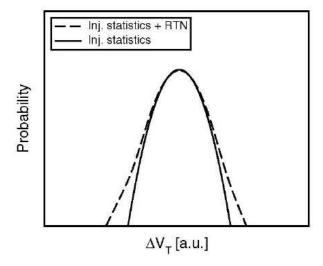

| 1.13 | Probability distributions of the injection statistics with and with- |    |

|      | out the contribution of the RTN (Random Telegraph Noise)             | 16 |

| 2.1  | Cross section of a PCM cell (left) and its relative graphic repre-   |    |

| 2.1  | sentation (right)                                                    | 19 |

|      | sentation (ngit)                                                     | エフ |

LIST OF FIGURES v

| 2.2  | Typical PCM array topology with $pnp$ bipolar transistors as a se-                 |    |

|------|------------------------------------------------------------------------------------|----|

|      | lecting element                                                                    | 20 |

| 2.3  | Waveforms applied to each cell in the array to perform the dy-                     |    |

|      | namic $I-V$ characterization and the extraction of $R_{set}$ and $V_{th}$          | 22 |

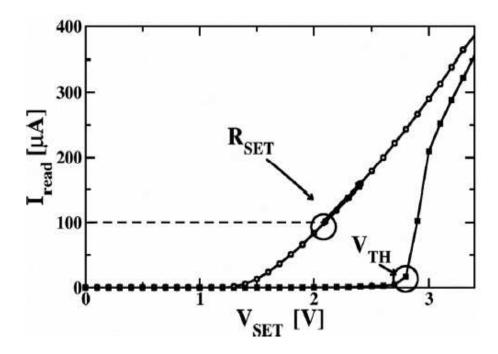

| 2.4  | Result of the dynamic $I-V$ characterization. The two curves on                    |    |

|      | display are the average over the whole cell population                             | 23 |

| 2.5  | R-I characterization. The curve on display represents the aver-                    |    |

|      | age over the whole cell population                                                 | 24 |

| 2.6  | Distribution of $V_{T1}$ , $V_{T2}$ , $V_s$ , parameters in a Gaussian probability |    |

|      | plot                                                                               | 24 |

| 2.7  | Average value of $V_s$ versus the wordline index. Each point is the                |    |

|      | average over the columns belonging to the considered wordline                      | 25 |

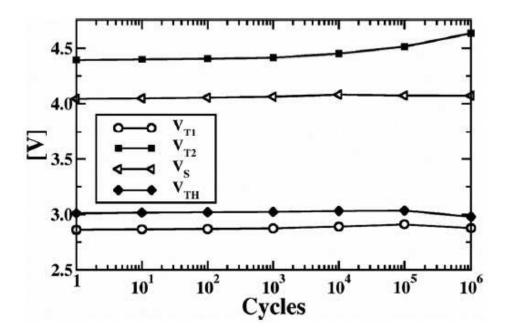

| 2.8  | Average values of $V_{th}$ , $V_{T1}$ , $V_{T2}$ and $V_s$ during cycling          | 25 |

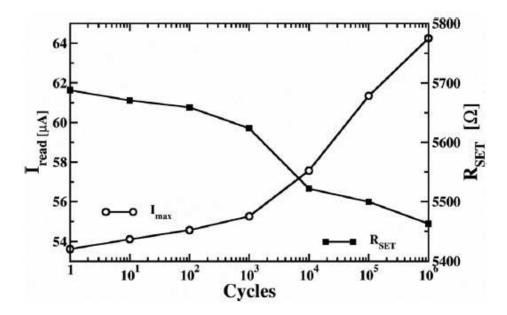

| 2.9  | Average values of $I_{max}$ , and $R_{set}$ during cycling                         | 26 |

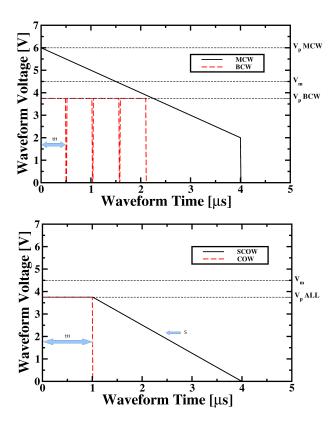

| 2.10 | a): MCW and BCW waveforms; b): SCOW and COW waveforms.                             | 31 |

| 2.11 | Logical flow used for waveforms optimization process                               | 31 |

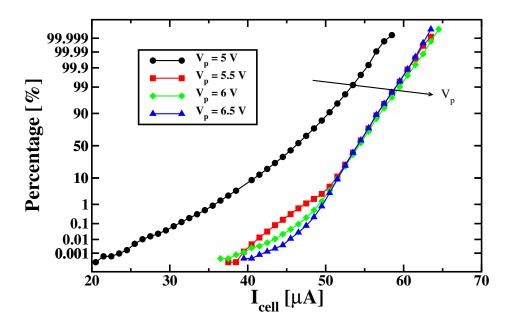

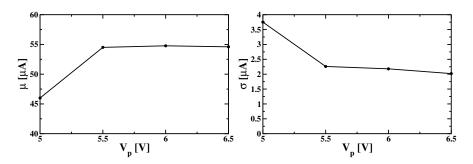

| 2.12 | $I_{cell}$ distribution dependency on $V_p$ applied within a MCW                   | 32 |

| 2.13 | a): Variation of $\mu$ criterion on MCW, in relation to $V_p$ b): Variation        |    |

|      | of $\sigma$ criterion on MCW, in relation to $V_p$                                 | 32 |

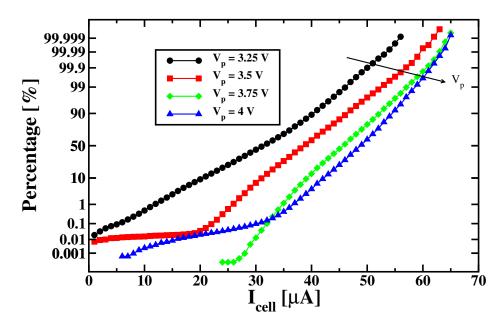

| 2.14 | $I_{cell}$ distribution dependency by applied $V_p$ within SCOW. Similar           |    |

|      | distribution are obtained using COW                                                | 33 |

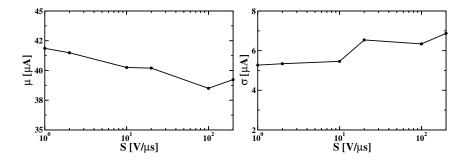

| 2.15 | a): Variation of $\mu$ criterion on SCOW, in relation to $S$ (log-scaled)          |    |

|      | b): Variation of $\sigma$ criterion on SCOW, in relation to $S$ (log-scaled).      | 33 |

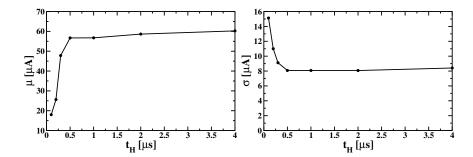

| 2.16 | a): Variation of $\mu$ criterion on COW, in relation to $t_H$ b): Variation        |    |

|      | of $\sigma$ criterion on COW, in relation to $t_H$ .                               | 34 |

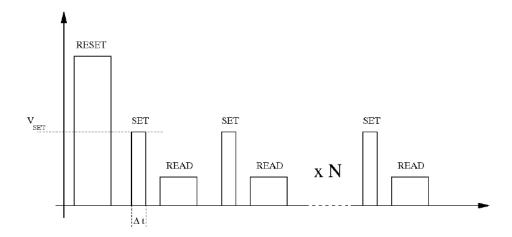

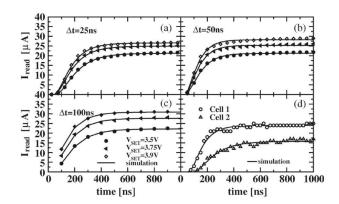

| 2.17 | Sequence of pulses used for the experiments. The SET pulse con-               |    |

|------|-------------------------------------------------------------------------------|----|

|      | ditions have been: $\Delta t$ =(10ns), 25ns, 50ns and 100ns; $V_{SET}$ =3.5V, |    |

|      | 3.75V, 3.9V. A total number of SET pulses $N$ has been applied                | 35 |

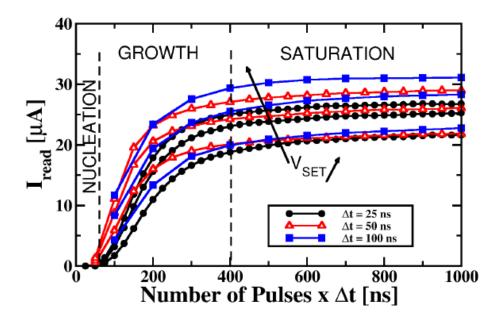

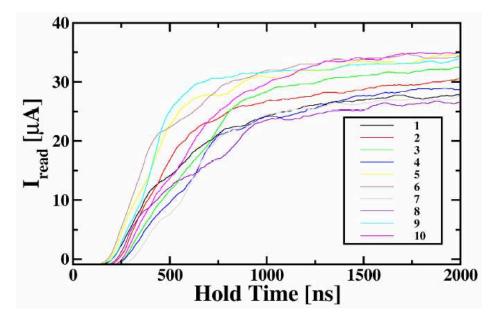

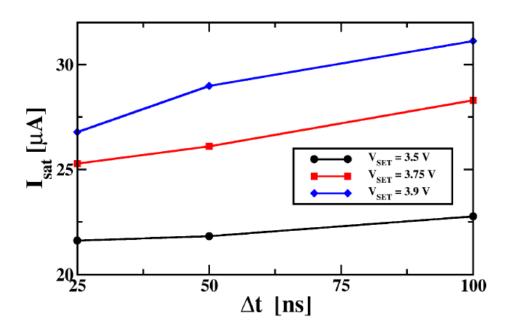

| 2.18 | Average read current for each operating condition                             | 36 |

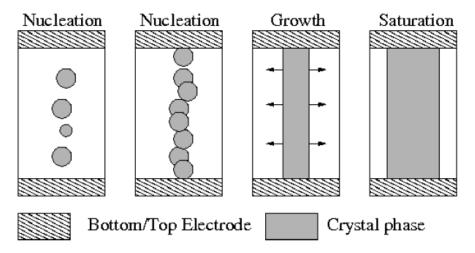

| 2.19 | Picture of the stages of the crystalline shunt formation and devel-           |    |

|      | opment                                                                        | 36 |

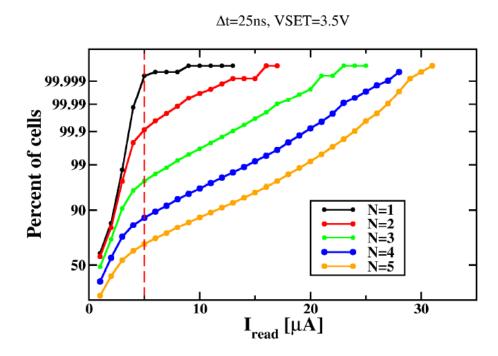

| 2.20 | Read current distributions after the first 5 SET pulses                       | 37 |

| 2.21 | SET curves for the same cell measured 10 consecutive times                    |    |

|      | ( $\Delta t$ =10ns)                                                           | 37 |

| 2.22 | Average saturation current as a function of the operating conditions.         | 39 |

| 2.23 | Read current distributions for each pulse duration                            | 39 |

| 2.24 | Read current distributions for each SET voltage                               | 39 |

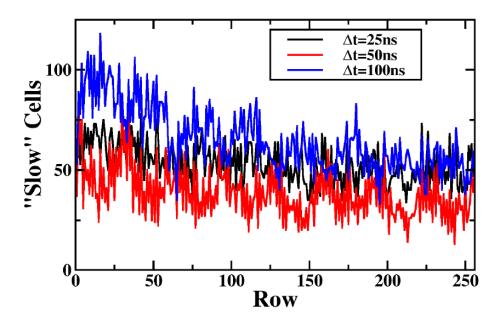

| 2.25 | Number of Slow cells as a function of their wordline (row) posi-              |    |

|      | tion within the array                                                         | 40 |

| 2.26 | Conductive GST model (left) and equivalent read path circuit (right).         | 40 |

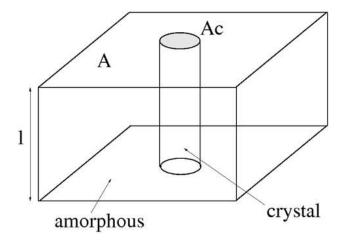

| 2.27 | Conductive GST model. A cylindric crystalline shunt approxima-                |    |

|      | tion is used for model compactness                                            | 42 |

| 2.28 | Model output on different SET operative conditions                            | 44 |

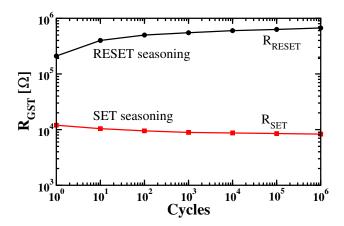

| 2.29 | Seasoning effect as a function of cycles number, evidenced as an              |    |

|      | increase of the average (on 512 Kbits cells) $R_{\it RESET}$ and a de-        |    |

|      | crease of $R_{SET}$                                                           | 45 |

| 2.30 | Equivalent R-I characteristic of the PCM array. Characterization              |    |

|      | data were retrieved from cycle 1 to $10^6$                                    | 46 |

LIST OF FIGURES vii

| 2.31 | PCM cell model for measurements and connection to the array.                 |    |

|------|------------------------------------------------------------------------------|----|

|      | The voltage drop on the bitline MOS selector and on BJT cell                 |    |

|      | selector is accounted                                                        | 47 |

| 2.32 | Waveform sequences for cycling with different erasing schemes                |    |

|      | in seasoning investigation experiments. Used erasing schemes                 |    |

|      | are depicted: MCW (solid), COW (dashed) and SCOW (dotted).                   |    |

|      | Waveforms parameters such as $V_p$ , $t_H$ and $S$ are also evidenced. $\ .$ | 48 |

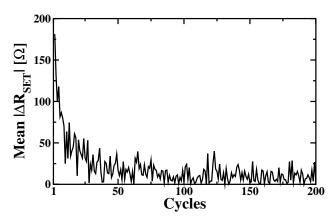

| 2.33 | Average variation of the array $R_{\it SET}$ calculated in modulus as the    |    |

|      | difference between two consecutive cycles measurements                       | 48 |

| 2.34 | Seasoning effect evaluated on consecutive single cell measurements.          | 49 |

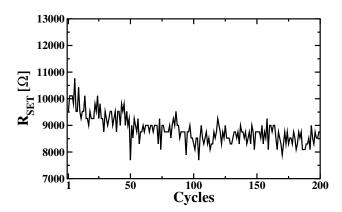

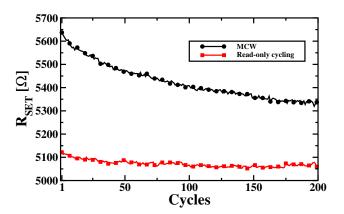

| 2.35 | S Average array $R_{SET}$ measured with a MCW erasing scheme. A              |    |

|      | comparison with the reference read only cycling is reported                  | 50 |

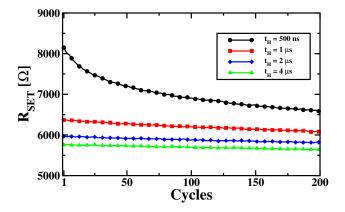

| 2.36 | Average array $R_{SET}$ measured with a COW erasing scheme. A                |    |

|      | dependance of the reduction of the $R_{\mathit{SET}}$ by the waveform pa-    |    |

|      | rameter $t_H$ is evidenced                                                   | 50 |

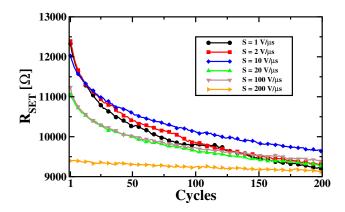

| 2.37 | Average array $R_{SET}$ measured with a SCOW erasing scheme. A               |    |

|      | dependance of the reduction of the $R_{\mathit{SET}}$ by the waveform param- |    |

|      | eter $S$ is evidenced                                                        | 51 |

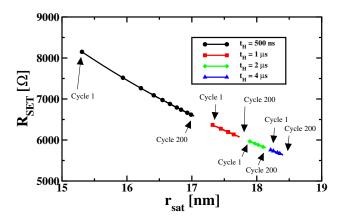

| 2.38 | S Average array $R_{SET}$ dependency from $r_{sat}$ within a COW eras-       |    |

|      | ing scheme with two different $t_H$ used. Cycle dependence is also           |    |

|      | evidenced                                                                    | 53 |

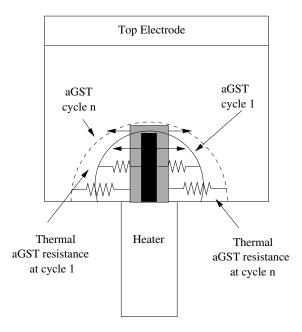

| 2.39 | PCM cell structure evidencing the seasoning phenomenon both in               |    |

|      | RESET and SET state                                                          | 53 |

LIST OF FIGURES viii

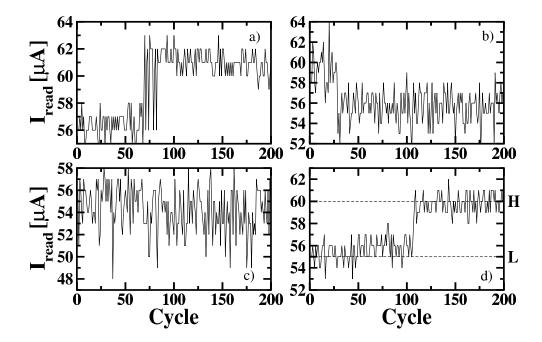

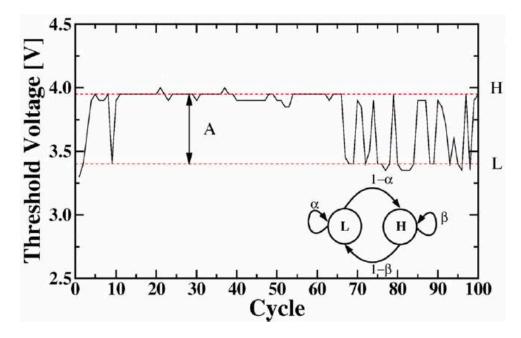

| 2.40 | Example of RTN-like behaviors in four PCM cells observable by                           |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | plotting $I_{read}$ after the Erase operation versus the number of cy-                  |    |

|      | cles. Two levels are evidenced (i.e. $H$ and $L$ in fig. $d$ ) representing             |    |

|      | the presence/absence of the secondary path                                              | 54 |

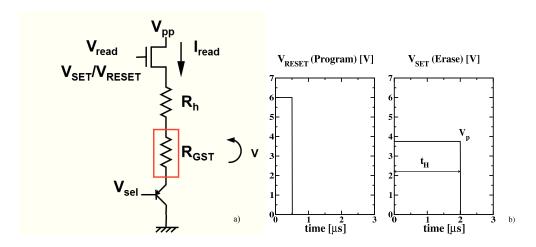

| 2.41 | a) Equivalent read/write path circuit of a PCM cell. b) Program                         |    |

|      | (RESET) and Erase (SET) waveforms exploited in this work                                | 55 |

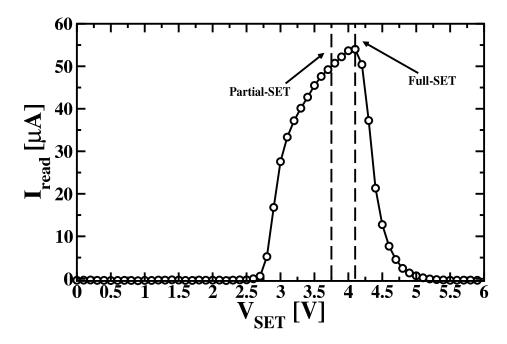

| 2.42 | Average $I_{read}$ versus $V_{SET}$ characteristic. As shown, $V_{SET}$ =               |    |

|      | 3.75V holds the active material in a Partial-SET state                                  | 56 |

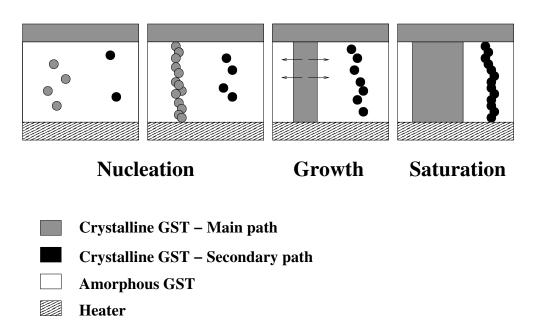

| 2.43 | Schematic description of the secondary path creation kinetics.                          |    |

|      | During the growth stage of the main percolation path, new GST                           |    |

|      | crystallite grains may nucleate and subsequently join together,                         |    |

|      | contributing to the secondary path formation                                            | 57 |

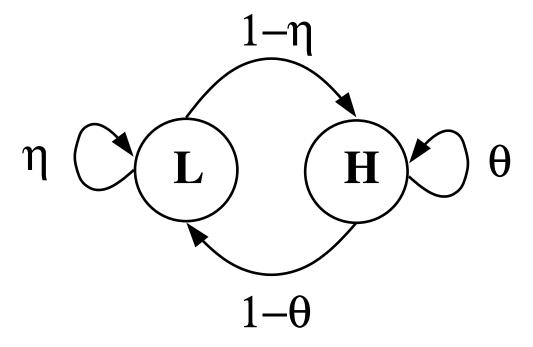

| 2.44 | Two-states Markov chain used for modeling the secondary path                            |    |

|      | presence/absence condition in PCM cells, where $\eta$ and $\theta$ represent            |    |

|      | the probability of remaining in the L and H status, respectively                        | 58 |

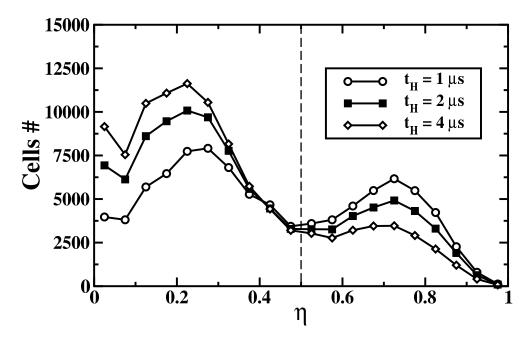

| 2.45 | Distribution of the probabilities $\boldsymbol{\eta}$ of remaining in the $L$ state for |    |

|      | three pulse durations $t_{\cal H}$ of the Erase operation. The cells popu-              |    |

|      | lation prone to create the secondary shunt is identified by the first                   |    |

|      | Gaussian peak with $\eta < 0.5.$                                                        | 59 |

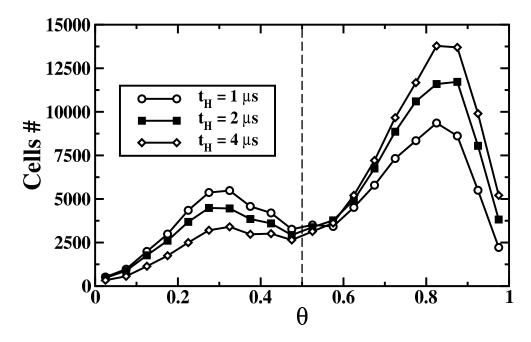

| 2.46 | Distribution of the probabilities $\theta$ of remaining in the $H$ state for            |    |

|      | three pulse durations $t_H$ of the Erase operation                                      | 60 |

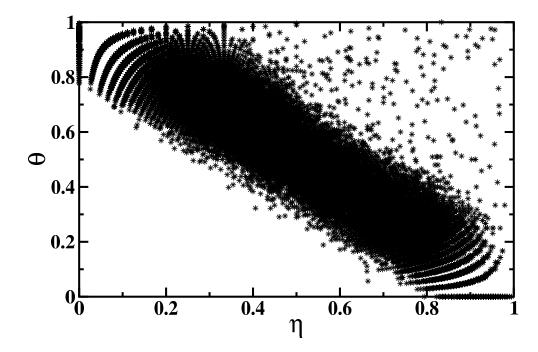

| 2.47 | Scatter plot of $\eta$ versus $\theta$ state probabilities for $t_H$ = $2\mu s$ (sim-   |    |

|      | ilar results are achieved for other pulse durations). The points                        |    |

|      | accumulates in the center of the plot clearly evidencing a linear                       |    |

|      | correlation between the two probability coefficients                                    | 61 |

LIST OF FIGURES ix

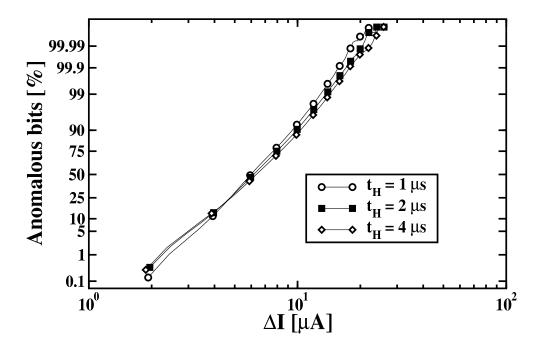

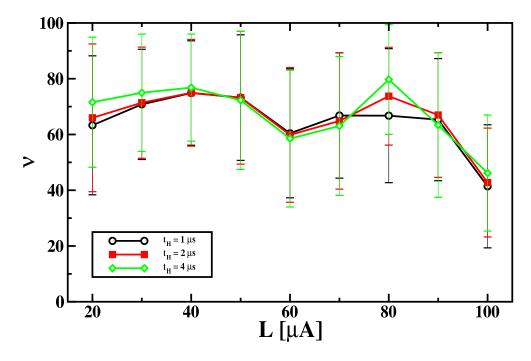

| 2.48 | Log-normal probability plot of the $\Delta I$ distribution                            | 62 |

|------|---------------------------------------------------------------------------------------|----|

| 2.49 | Numbers of state transitions for any set of cells characterized by                    |    |

|      | the same average $L$ level within 200 program/erase cycles for the                    |    |

|      | three erasing times $t_H$ . Symbols denote the average number of                      |    |

|      | state transitions, whereas the error bars represent the standard de-                  |    |

|      | viation from the mean value                                                           | 63 |

| 2.50 | $\Delta I$ shifts for any set of cells characterized by the same average $L$          |    |

|      | level within 200 program/erase cycles for the three erasing times                     |    |

|      | $t_H$ . Symbols denote the average $\Delta I$ shift, where the error bars             |    |

|      | represent the standard deviation from the mean value                                  | 64 |

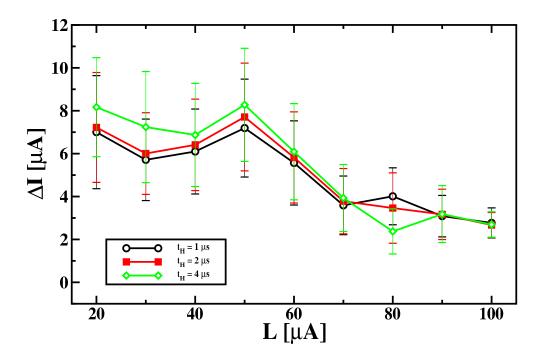

| 2.51 | Measured (symbols) and calculated (lines) $I_{read}$ tail distributions               |    |

|      | after 200 Program/Erase cycles for the three pulse durations. $t_{\rm H}$ =           |    |

|      | $1\mu s$ : circles and dotted line; $t_H$ = $2\mu s$ : squares and dashed line; $t_H$ |    |

|      | = $4\mu s$ : diamond and dashed/dotted line. The full line represents                 |    |

|      | the Gaussian Model behavior for $t_H$ = $2\mu s$ . Similar Gaussian be-               |    |

|      | havior are found for other $t_H$ values. The inset shows experimen-                   |    |

|      | tal data and fitting of the main part of the distribution for $t_H$ = $2\mu s$        |    |

|      | (the two other $t_H$ cases are almost superimposed)                                   | 66 |

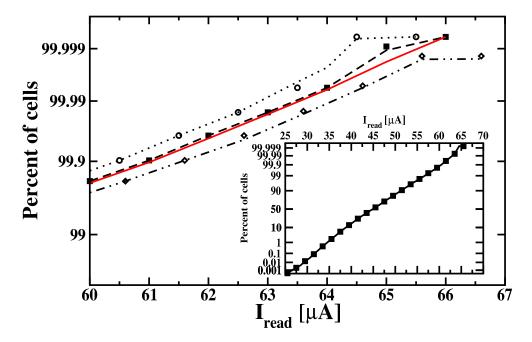

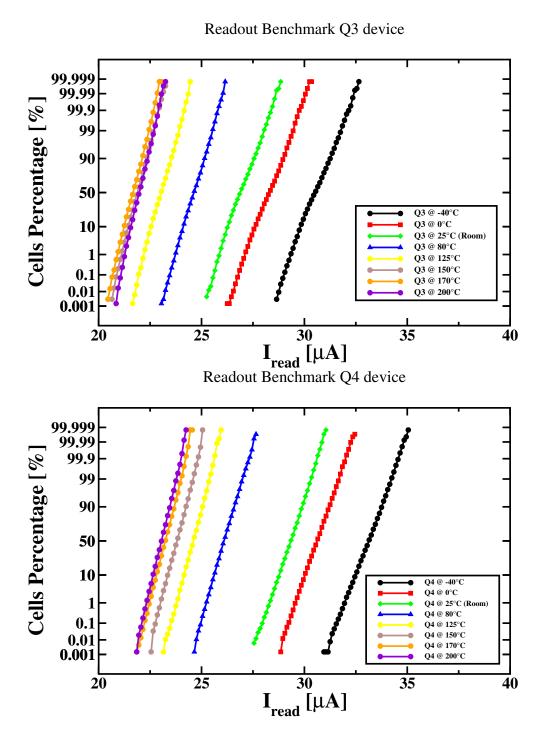

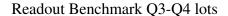

| 3.1  | Read characterization of SimpleEE modules lots                                        | 70 |

| 3.2  | Read benchmark between Q3 and Q4 device families                                      | 71 |

| 3.3  | Extracted SimpleEE array output gain at different temperatures                        | 71 |

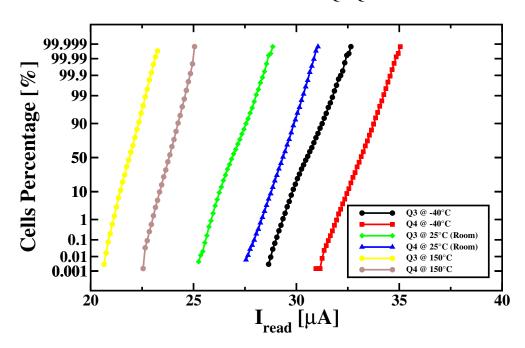

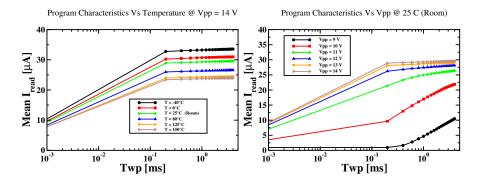

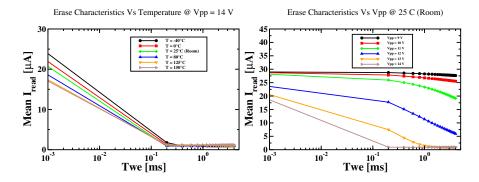

| 3.4  | Program characteristics of the memory with respect to working                         |    |

|      | temperature (left) and voltage exploited (right).                                     | 72 |

LIST OF FIGURES x

| 3.5  | Erase characteristics of the memory with respect to working tem-     |    |

|------|----------------------------------------------------------------------|----|

|      | perature (left) and voltage exploited (right)                        | 72 |

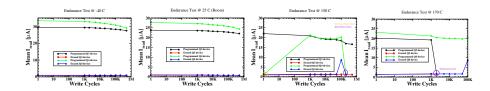

| 3.6  | Endurance characteristics of the memory modules at tempera-          |    |

|      | tures: -40°C, 25°C (room), 150°C and 170°C                           | 73 |

| 3.7  | Data retention characteristics of the memory modules at bake tem-    |    |

|      | peratures: 100°C, 150°C (room), 200°C and 250°C                      | 75 |

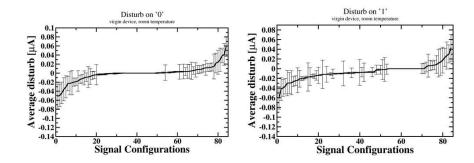

| 3.8  | Average disturb on the erased (left) and programmed (right) state    |    |

|      | for each signal configuration sorted in ascending order for a virgin |    |

|      | device                                                               | 77 |

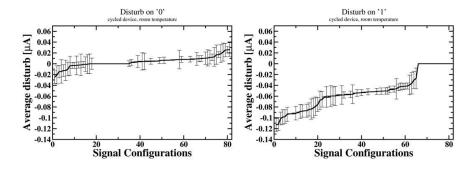

| 3.9  | Average disturb on the erased (left) and programmed (right) state    |    |

|      | for each signal configuration sorted in ascending order for a cy-    |    |

|      | cled device (500K cycles at room temperature)                        | 77 |

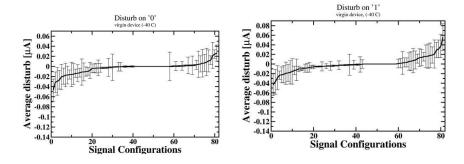

| 3.10 | Average disturb on the erased (left) and programmed (right) state    |    |

|      | for each signal configuration sorted in ascending order for a cy-    |    |

|      | cled device (500K cycles at room temperature)                        | 77 |

| 3.11 | Distributions before and after disturb application for a sample cy-  |    |

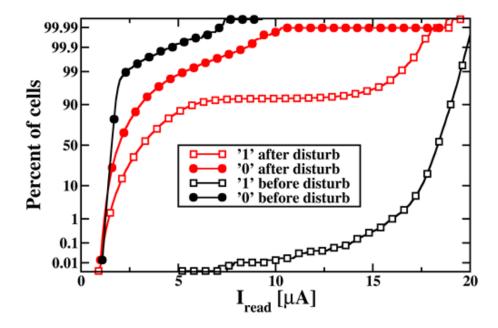

|      | cled at hot temperature (150°C) for 500K cycles                      | 78 |

| 3.12 | p-EEPROM cell architecture (left) and table summarizing normal       |    |

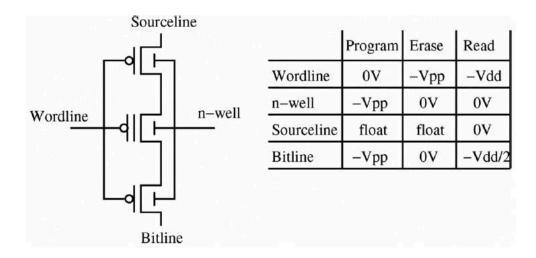

|      | operating conditions (right)                                         | 80 |

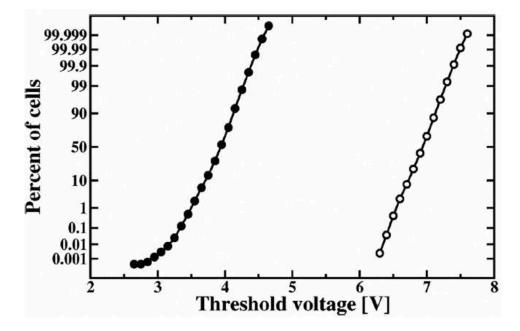

| 3.13 | Erased (left) and programmed (right) distribution of the Flash       |    |

|      | sample                                                               | 80 |

| 3.14 | Erased (left) and programmed (right) distribution of the p-          |    |

|      | EEPROM sample                                                        | 81 |

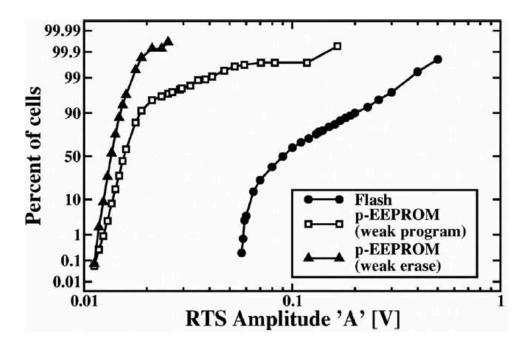

| 3.15 | Example of erratic cell in the Flash sample                          | 81 |

| 3.16 | Lognormal distribution of threshold voltage shift of erratic cells.  | 82 |

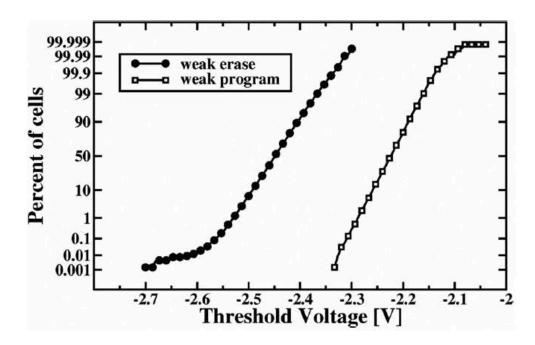

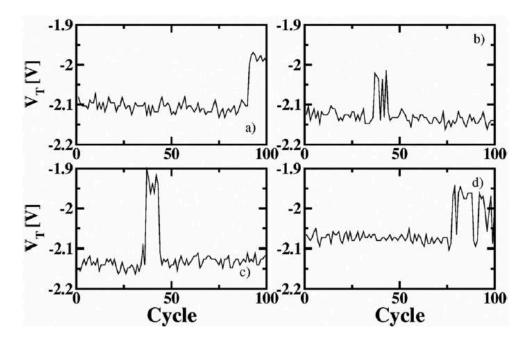

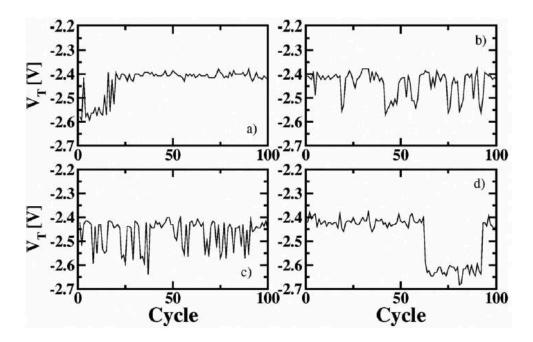

| 3.17 | Examples of erratic bits in p-EEPROM device after weak-                  |    |

|------|--------------------------------------------------------------------------|----|

|      | program operation during cycling                                         | 83 |

| 3.18 | Examples of erratic bits in p-EEPROM device after weak-erase             |    |

|      | operation during cycling                                                 | 84 |

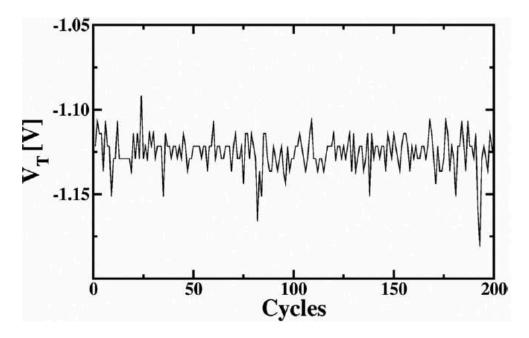

| 3.19 | ${\it V_{T}}$ of an arbitrary p-EEPROM cell monitored during cycling us- |    |

|      | ing standard program waveforms. The same behavior can be ob-             |    |

|      | served on different cells and for more cycles                            | 85 |

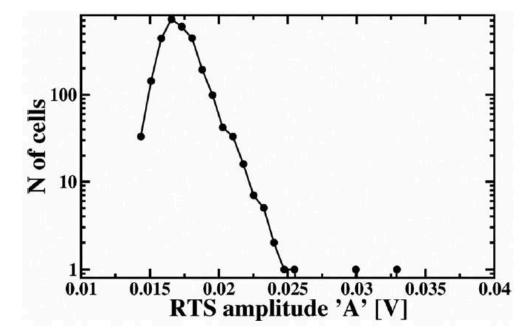

| 3.20 | Shift distribution of the erratic bits in p-EEPROM device                | 85 |

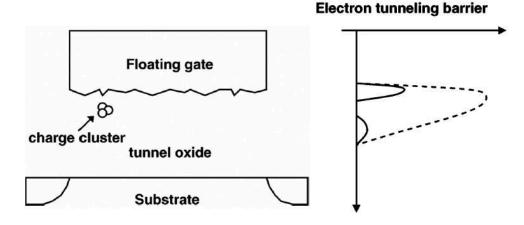

| 3.21 | Different values of energies are involved in the AHHI (Anode Hot         |    |

|      | Hole Injection) behavior of p-EEPROM and FLASH. In particu-              |    |

|      | lar, AHHI on FLASH is fed by higher energies with respect to             |    |

|      | p-EEPROM, thus inducing more erratic behaviors                           | 86 |

| 3.22 | Impact of the charge cluster on electron tunneling barrier               | 86 |

| 4.1  | Simple cantilever element for physical principles evaluation             | 91 |

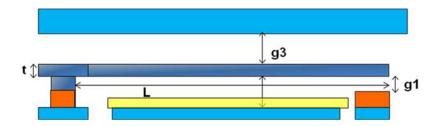

| 4.2  | The teeter-totter concept used as a MEMS switch in the arrays            |    |

|      | characterized in this work (top) and a TEM picture of its inte-          |    |

|      | gration (bottom). The geometrical dimension of the structure are         |    |

|      | evidenced                                                                | 95 |

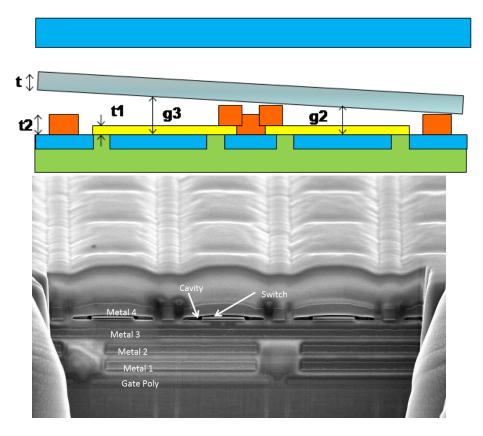

| 4.3  | Read window of a Nanomech eNVM array. In this sample a read              |    |

|      | window of more than four orders of magnitude is shown                    | 97 |

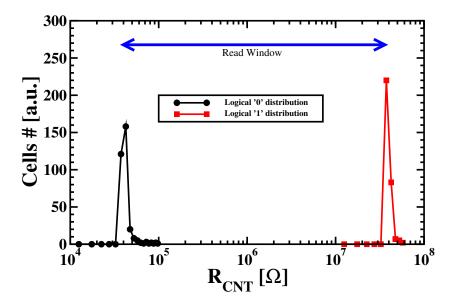

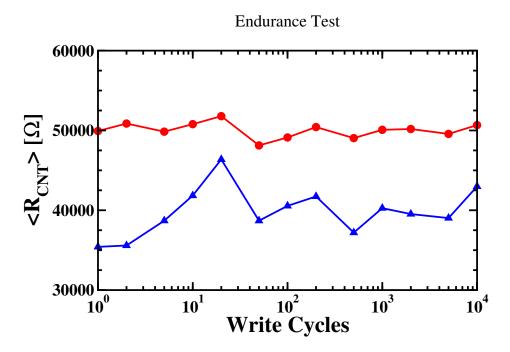

| 4.4  | Benchmark of the $\langle R_{CNT} \rangle$ between the room temperature  |    |

|      | endurance stress and the HTOL endurance stress                           | 98 |

LIST OF FIGURES xii

| 4.5  | Insight of the $\langle R_{CNT} \rangle$ characteristic under room temperature |

|------|--------------------------------------------------------------------------------|

|      | endurance stress (triangles) and under the HTOL endurance stress               |

|      | (squares)                                                                      |

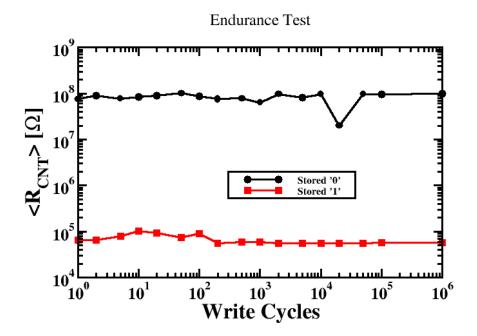

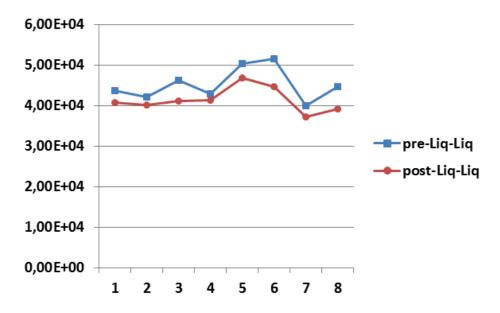

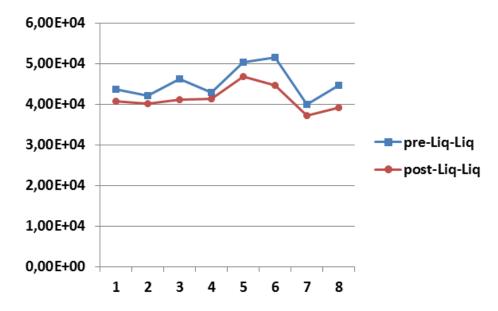

| 4.6  | $< R_{CNT} >$ monitoring during cumulative endurance experiment. 100           |

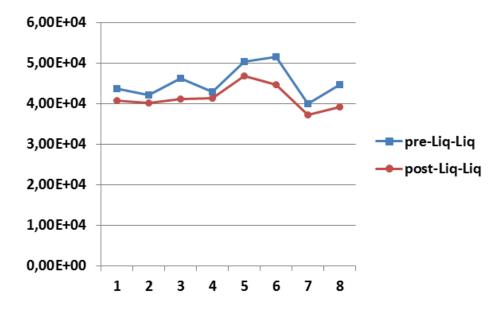

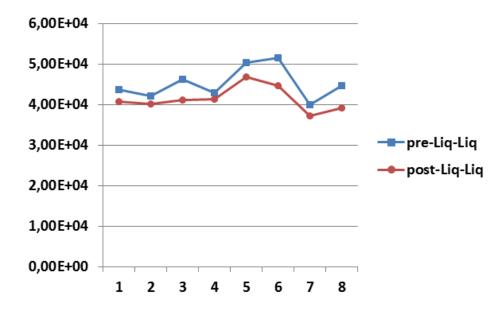

| 4.7  | $< R_{CNT} >$ measured for different architectures of Nanomech                 |

|      | eNVM. The values were calculated before and after the liquid-                  |

|      | liquid experiment                                                              |

| 4.8  | Reliability tests executed on NanoMEMS memories. No failing                    |

|      | bits                                                                           |

| 4.9  | Relative resistance drift, average across full array, for all relia-           |

|      | bility tests performed on 6 alternative MEMS switch architecture               |

|      | variations                                                                     |

| 4.10 | Contact resistance behavior on Liquid-Liquid test with -55C -                  |

|      | 150C temperature range. The distribution shows an improvement                  |

|      | of the $R_{CNT}$ after the test                                                |

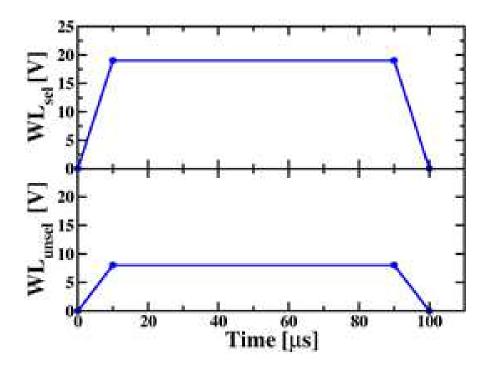

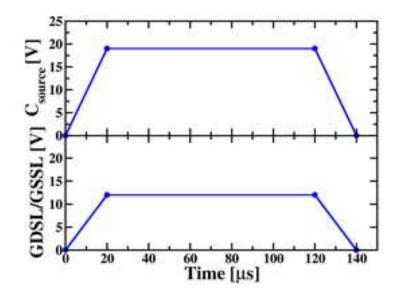

| 5.1  | Signals applied to the array for the program operation 109                     |

| 5.2  | Signals applied to the array for the erase operation                           |

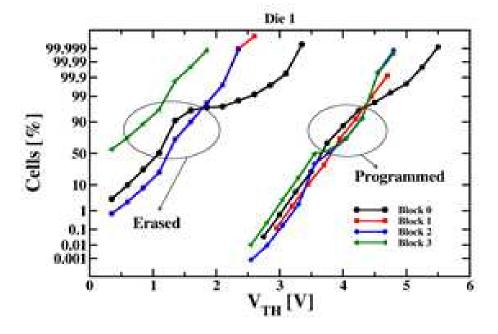

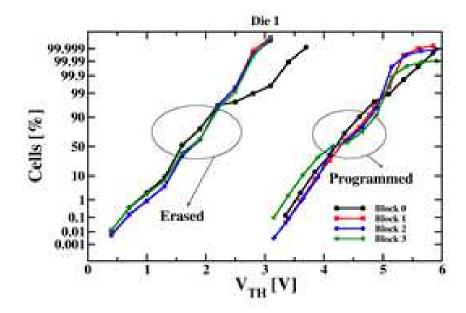

| 5.3  | Program and erase distributions measured using $I_{ref}$ =200nA 110            |

| 5.4  | Program and erase distributions measured using $I_{ref}$ =400nA 111            |

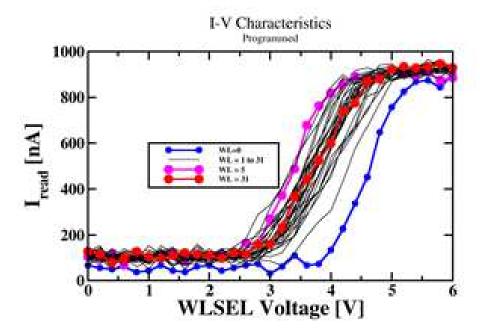

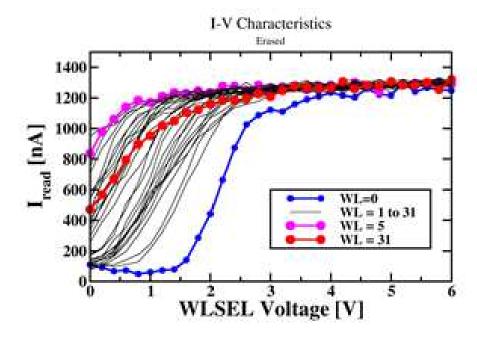

| 5.5  | I-V characteristics on the programmed state of an arbitrary array              |

|      | string                                                                         |

| 5.6  | I-V characteristics on the erased state for same string                        |

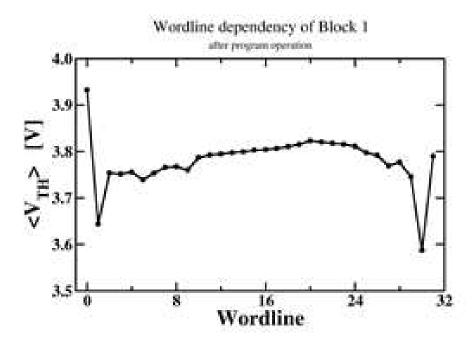

| 5.7  | Wordline average threshold voltage dependency                                  |

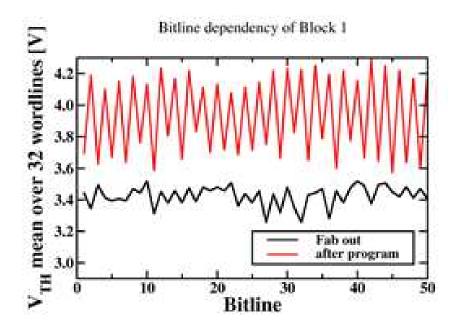

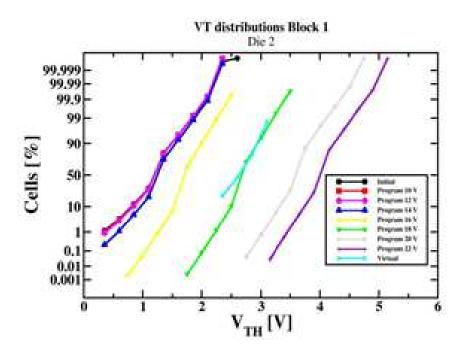

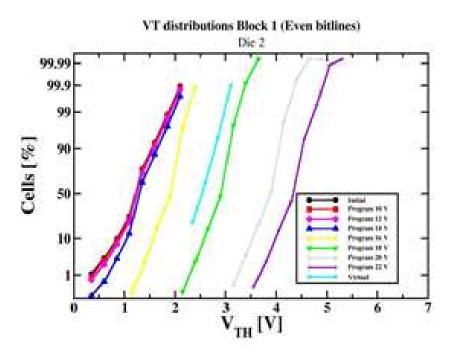

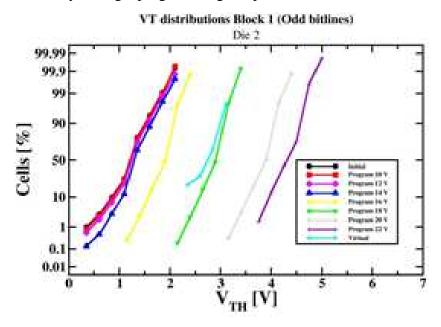

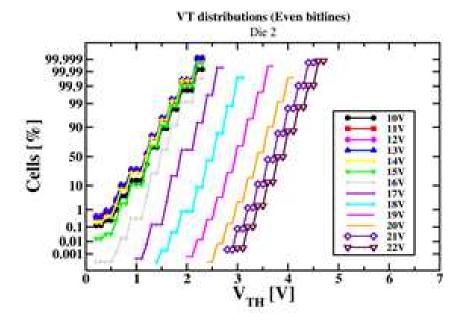

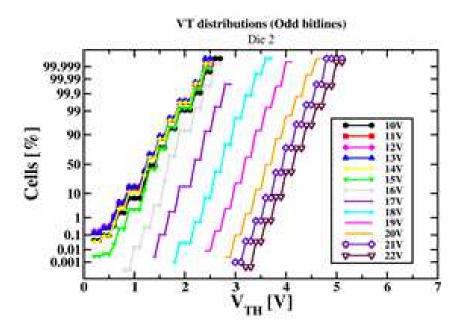

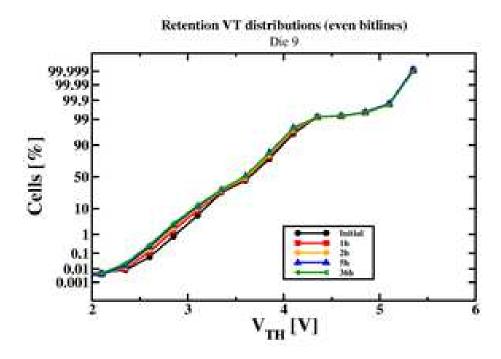

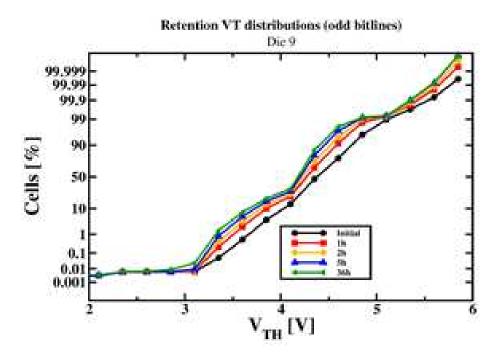

| 5.8  | Bitline even/odd behavior evidenced on wordline average thresh-           |  |

|------|---------------------------------------------------------------------------|--|

|      | old voltage                                                               |  |

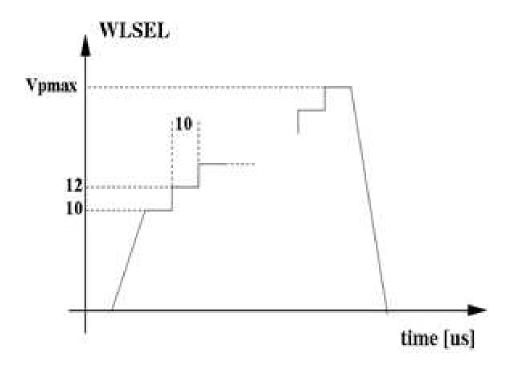

| 5.9  | Staircase programming waveform                                            |  |

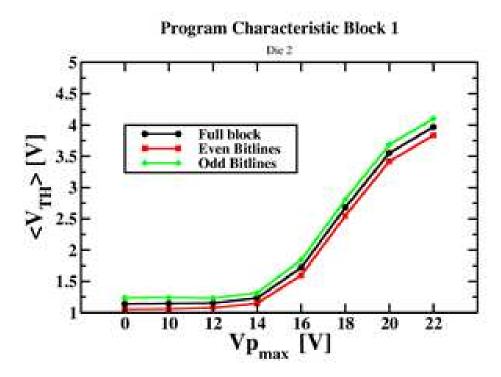

| 5.10 | Single block average program characteristic. Even/Odd bitlines            |  |

|      | separate contributions have been evidenced                                |  |

| 5.11 | Evolution of the threshold voltage distributions of an entire array       |  |

|      | block during a programming ramp                                           |  |

| 5.12 | Evolution of the threshold voltage distributions of cells belonging       |  |

|      | to even bitlines only during a programming ramp                           |  |

| 5.13 | Evolution of the threshold voltage distributions of cells belonging       |  |

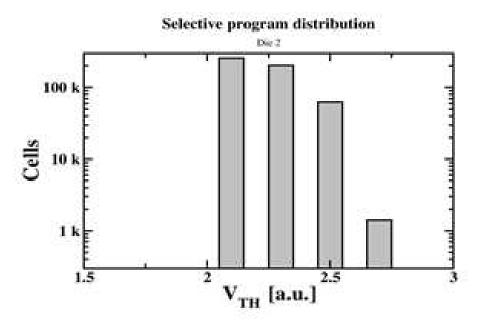

|      | to odd bitlines only during a programming ramp                            |  |

| 5.14 | Cells number belonging to a threshold voltage bin after applica-          |  |

|      | tion of the post-analysis data compactation                               |  |

| 5.15 | Threshold voltage distribution using the ramped waveform with 1           |  |

|      | V steps on even bitlines                                                  |  |

| 5.16 | Threshold voltage distribution using the ramped waveform with 1           |  |

|      | V steps on odd bitlines                                                   |  |

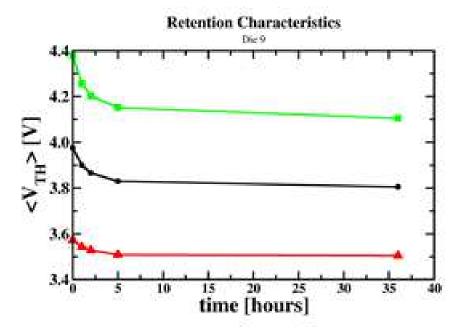

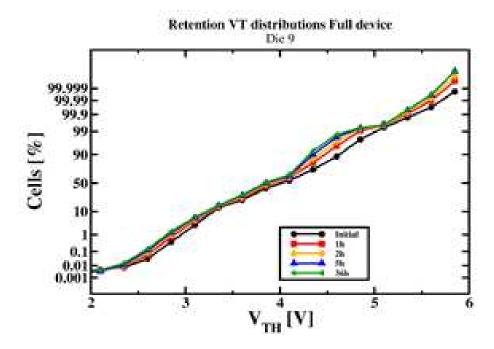

| 5.17 | Retention characteristics of the array. The average retention of          |  |

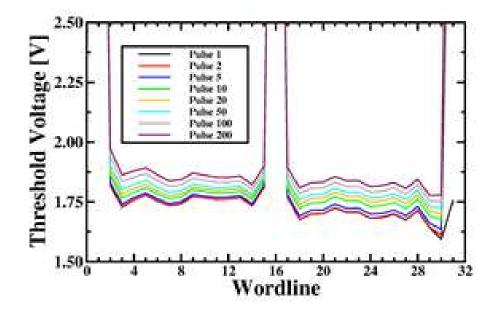

|      | the whole array, the average retention of even bitlines only and          |  |

|      | the average retention of odd bitlines only are evidenced by black,        |  |

|      | green and red curves respectively                                         |  |

| 5.18 | Threshold voltage distribution of the full device in RTB experiments. 123 |  |

| 5.19 | Threshold voltage distribution of the array even bitlines in RTB          |  |

|      | experiments                                                               |  |

| 5.20 | Threshold voltage distribution of the array odd bitlines in RTB                                 |

|------|-------------------------------------------------------------------------------------------------|

|      | experiments                                                                                     |

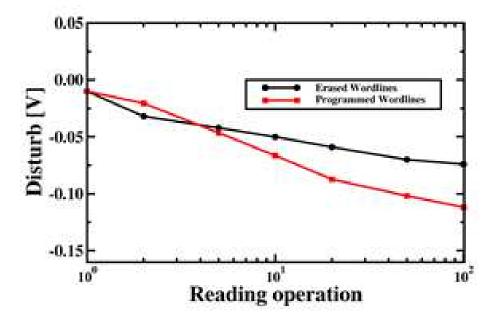

| 5.21 | Impact of read disturb on both programmed and erased cells 125                                  |

| 5.22 | Threshold voltage measured after 1, 2, 5,, 200 program pulses                                   |

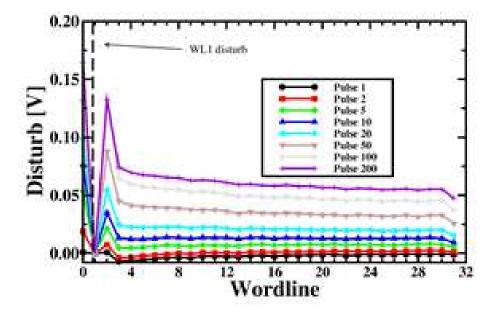

|      | applied simultaneously on WL1, WL16, and WL30 126                                               |

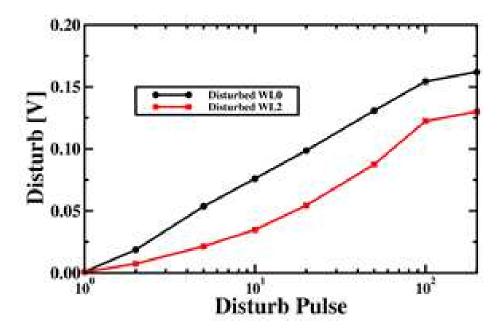

| 5.23 | Net effect (disturb) of a program disturb measured after 1, 2, 5,,                              |

|      | 200 disturb pulses applied on WL1                                                               |

| 5.24 | Evolution of disturb on WL0 and WL2 with the number of pro-                                     |

|      | gram disturb pulses applied to WL1                                                              |

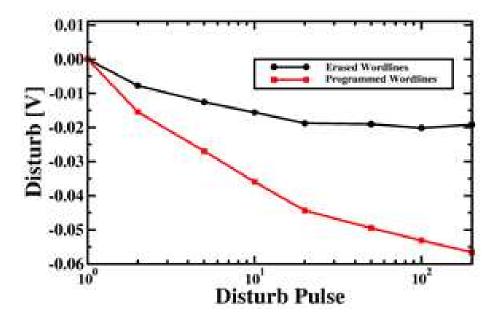

| 5.25 | Block to block interference evaluated by monitoring both pro-                                   |

|      | grammed and erased cells while applying program disturb pulses                                  |

|      | on WL33 of an adjacent block                                                                    |

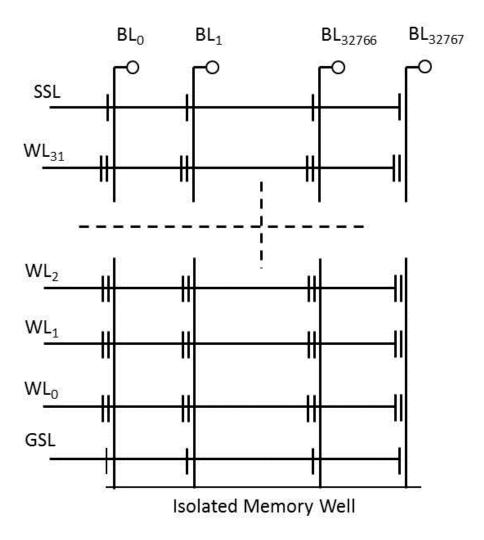

| 5.26 | Standard NAND array architecture. The figure represents a single                                |

|      | block of the CT array considered in this analysis                                               |

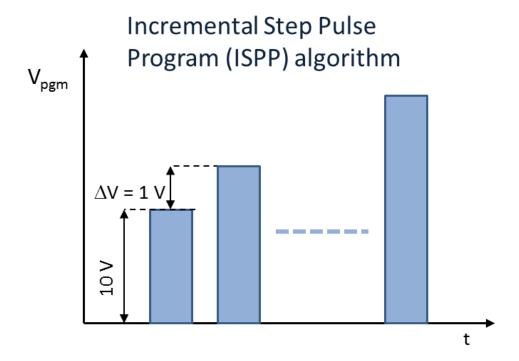

| 5.27 | ISPP Pulse characteristics exploited in this work. The duration                                 |

|      | per pulse is $4\mu$ s                                                                           |

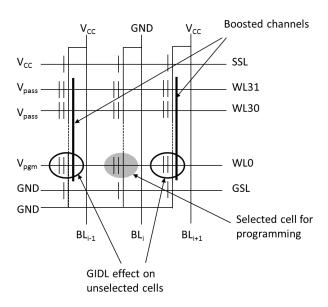

| 5.28 | Bias conditions possibly activating the GIDL effect from GSL                                    |

|      | transistors belonging to columns $BL_{i-1}$ and $BL_{i+1}$                                      |

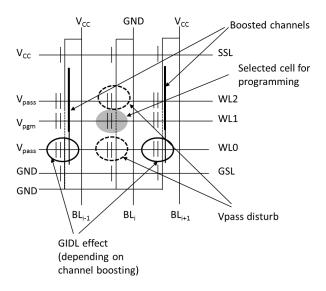

| 5.29 | Bias conditions possibly activating the GIDL effect from GSL                                    |

|      | transistors belonging to columns $\mathrm{BL}_{i-1}$ and $\mathrm{BL}_{i+1}$ and the $V_{pass}$ |

|      | disturb in unselected cells belonging to columns $BL_i$                                         |

LIST OF FIGURES xv

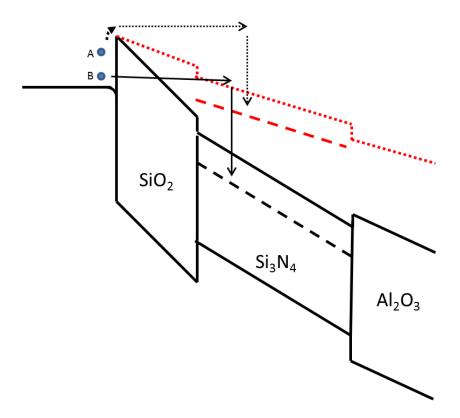

| 5.30 | Band structure of the CT cells (excluding the TaN/Ti/TaN metal          |

|------|-------------------------------------------------------------------------|

|      | gate) considered in this work. For high biases electron B is free to    |

|      | tunnel into $SiO_2$ and then gets trapped into $Si_3N_4$ layer. For low |

|      | biases electron A is still able to get trapped, although the energy     |

|      | levels of the bands are shifted upwards                                 |

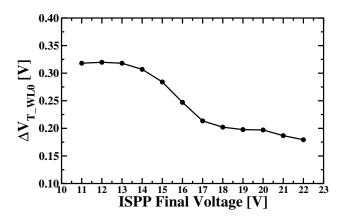

| 5.31 | EWD dependence on the exploited ISPP voltages during a pro-             |

|      | gram operation. $V_{pass}$ has been fixed at 8 V for the unselected     |

|      | wordlines                                                               |

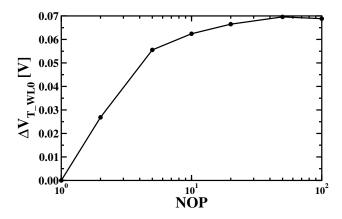

| 5.32 | EWD dependence on the number of performed NOP on WL1.                   |

|      | $V_{pass}$ has been fixed at 8 V for the unselected wordlines 135       |

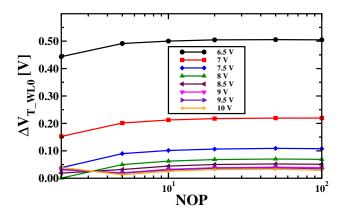

| 5.33 | EWD as a function of the NOP number. $V_{pass}$ has been varied in      |

|      | order to evaluate the dependence of the phenomenon on the pass          |

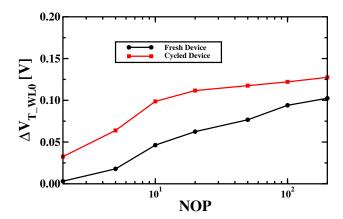

|      | voltage                                                                 |

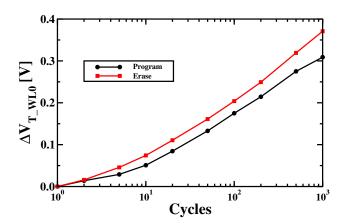

| 5.34 | EWD dependence on the number of write cycles performed on the           |

|      | CT NAND array                                                           |

| 5.35 | EWD as a function of the NOP number. A dependence on the                |

|      | device aging is evidenced. $V_{pass}$ has been fixed to 8 V for the     |

|      | unselected wordlines                                                    |

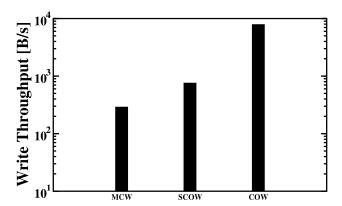

| A.1  | Calculated write throughput comparison between the different            |

| 71.1 | erasing schemes applied within a PCM                                    |

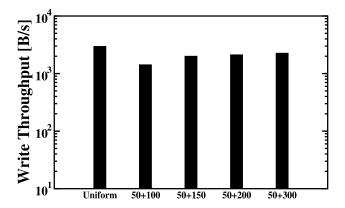

| A.2  | Mean write throughput calculated with different writing scenar-         |

| 11.2 | ios. The uniform traffic condition is compared with 50 writings         |

|      | ·                                                                       |

|      | on the data reliable area and 100, 150, 200, 300 writings on the        |

|      | high speed area                                                         |

|                 | •   |

|-----------------|-----|

| LIST OF FIGURES | XV1 |

|                 |     |

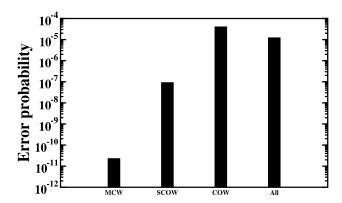

| A.3 | Error probability comparison between single PCM data partitions |  |  |

|-----|-----------------------------------------------------------------|--|--|

|     | and PCM comprising the whole array                              |  |  |

## **List of Tables**

| 2.1         | Comparison resume of the analyzed waveforms                             | 32  |

|-------------|-------------------------------------------------------------------------|-----|

| 2.2         | Seasoning impact resume with different waveform                         | 51  |

| 2.3         | Parameters used for the statistical modeling of the gaussian part       |     |

|             | of the $I_{read}$ distributions extracted from the experimental data at |     |

|             | cycle 1                                                                 | 62  |

| 2.4         | Parameters used for the fitting of the bimodal gaussian distribu-       |     |

|             | tions of $\eta$ and $\theta$ state probability                          | 65  |

| 2.5         | Parameters used for the calculation of the $\Delta I_i$ shift           | 65  |

| <b>A</b> .1 | Erasing schemes comparison resume                                       | 144 |

## **Chapter 1**

#### Introduction

The last decade of research in non-volatile memories, both from academic and industrial perspective, arose potential threats to the so-called "happy scaling" era, where the only way to achieve memory density, performance and enhanced reliability exploited a furious geometrical shrinking of the memory cells dimensions.

The mainstream for non-volatile memory technology in these years has been represented by the floating gate-based memories such as NOR and NAND Flash. These memories relies on a manufacturing process and on a physical storage solution which reached so far the maturity level. Indeed, both kind of Flash architectures are reliably used either as a code memory (NOR Flash) for storing BIOS, applications and operating systems for mobile environments or as a data memory (NAND Flash) relying on the high storage capacity offered by these memories. The NAND Flash market segment gained particular momentum during these decades thanks to the blast of the portable applications such as digital cameras, smartphones, mp3 players, an so on. Unfortunately, these largely used components in embedded systems and MPSoCs (Multi Processing System on Chip) are

facing difficulties in keeping up the performances and the reliability requested by a non-volatile memory components.

That explain the gained interest in these years on the so-called universal memories which represent the intersection between the performances of the traditional semiconductor volatile memories such as DRAM and SRAM and the reliability offered by a non-volatile technology. The 2010 global market for emerging non-volatile random access memory products was projected to have reached 115 million USD. This market will increase to 1,590 million USD by 2015 showing an average annual growth rate of 69% per year from 2010 to 2015. In this thesis several innovative memory concepts will be analyzed as potential alternative to Flash technology. To name few of them it has been studied the Phase Change memories, SimpleEE memories, NanoMEMS memories and Charge Trapping memories.

Now it will provided a quick overview on what are the intrinsic limit of the floating gate technology and what are the emerging issues that are forcing system designers to change their mind in favor of such innovative memory technologies.

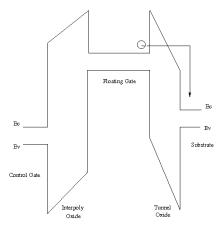

#### 1.1 Intrinsic Flash reliability limits

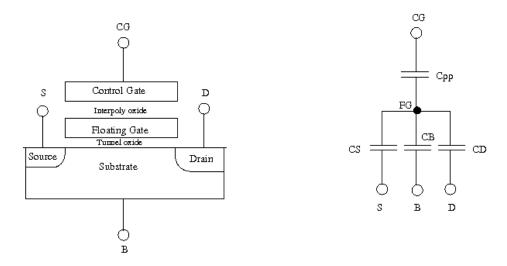

The concept element of traditional Flash memory cell is a metal oxide semiconductor device with a floating gate electrically isolated by means of a tunnel oxide and of an interpoly oxide as sketched in Fig.1.1 [1]. The former oxide plays a basic role for the control of the device threshold voltage whose value represents, from a physical point of view, the stored information. Electrons transferred into the floating gate give a threshold voltage variation  $\Delta VT = \frac{-Q}{Cpp}$ . In quiescent conditions, thanks to the two oxides, the charge stored should not leak away, thus granting

the nonvolatile paradigm fulfillment. Oxides are available in different material depending on the Front End of Line (FEOL) process. The common materials are: pure silicon dioxide ( $SiO_2$ ) for tunnel oxides and a stack of Oxide-Nitride-Oxide ( $SiO_2$ - $Si_3N_4$ - $SiO_2$ ) for interpoly oxides.

Figure 1.1: FLOTOX device and its equivalent capacitance model.

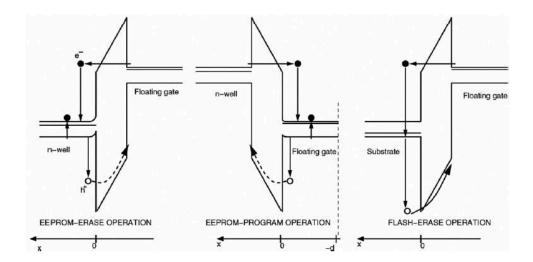

The cells are rearranged into an array organization [2] in which we can define three basic subdimensions: string, page and block. The physical mechanism used for both injecting and extracting electrons to/from the floating gate is the Fowler-Nordheim (FN) tunneling [3]. High electrical field applied to the tunnel oxide (FOX is almost 10 MV/cm) allows for electron transfer across the thin insulator to the floating gate. In NAND architectures the electronic tunneling involves the MOS channel/substrate and requires appropriate biasing of control gate and bulk terminals (see Fig.1.2), while drain and source are left floating. With respect to the Channel Hot Electron mechanism exploited for cell programming in NOR architectures, FN tunneling requires higher voltages, therefore much more complex charge pumps and higher programming times. In addition, the use of the same

mechanism for both programming and erasing the cells exposes the tunnel oxide to a larger degradation, with possible reliability effects. These drawbacks, however, are compensated by the much lower current (orders of magnitudes) required by the writing operations significantly improving power consumption and/or programming parallelism.

Figure 1.2: Band diagram sketch of tunneling effect.

During its lifetime a Flash module undergoes a large number of Program/Erase cycles. Every cycle involves very high electrical fields applied to the tunnel oxide. The reliability of the entire memory requires that the tunnel oxide is able to operate correctly under stress conditions. It is obvious that huge efforts are to be spent to determine the right process for the tunnel oxide creation (in terms of thickness, material, growth, defectivity, interface, ) in order to achieve a successful and reliable Flash technology. However, the scaling of the geometries is not helping these efforts, most of the time forcing to consider new radical design

approaches.

The main reliability issues for Flash technology are represented by the endurance and the data retention features.

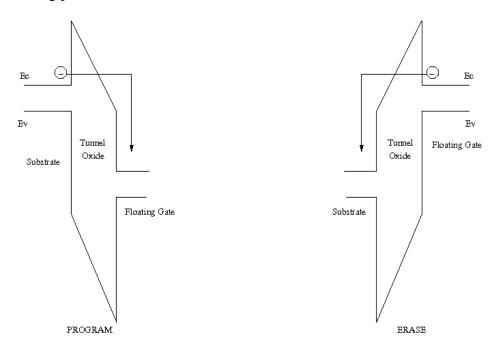

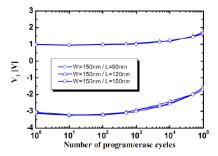

The endurance of a memory module is defined as the minimum number of Program/Erase cycles that the module can withstand before leading to a failure. The erased and programmed distributions must be suitably separated, in order to correctly read the logical state of a cell. The difference between EV (Erase reference Value) and PV (Program reference Value) is defined as the "read margin window". However, keeping a correct read margin is not sufficient to guarantee a correct read operation: if during its lifetime the threshold voltage of an erased cell exceeds the EV limit and approaches 0 V, the current flowing through the cell may be not high enough to be identified as "erased" by the reading circuitry, thus producing a read error. Similarly, a programmed cell could be read as "erased" if its threshold voltage becomes lower than PV and approaches 0 V. As for the programmed distribution, it is also important that the upper threshold limit does not increase significantly with time, since a too high threshold can block the current flowing through the strings during reading operations. FN tunneling leads intrinsically to oxide degradation [4]. As a result of consecutive electron tunneling, traps are generated into the oxide [5]. When filled by electrons, charged traps can increase the potential barrier thus reducing the tunneling current, as shown in Fig.1.3. Since the programming and erasing pulses feature constant amplitude and duration, less charge is transferred to and from the floating gate causing an efficiency reduction of both the program and erase operations. A narrowing of the read margin window is then expected. The charge trapped inside the oxide also produces a threshold shift  $\Delta VT$  directly proportional to its amount. The VT shift is symmetrical and increases the threshold voltage of both erased and programmed cells (see Fig. 1.4). Writing waveform optimization can help in limiting the trapped charge. For example, it has been shown that the window closure can be reduced by using low voltage erasing pulses able to remove the charge accumulated in the oxide. As shown in Fig.1.4, the threshold voltage shifts increase with the number of program/erase operations until an endurance failure occurs. Threshold voltage shifts could be recovered by applying specific procedures, that however result not convenient when comparing their effects with the required architectural overheads and time consumption. As evidenced in Fig.1.4, the most critical effect is the increase towards 0 V of the erased threshold. To check whether all cells of a sector have been correctly erased (all threshold voltage must be below 0 V), an erase verify procedure is applied after any erase operation. It consists in a particular read operation performed by driving simultaneously all the word lines of the sector at 0V: if the read current in a bitline is 0, it means that at least a cell blocked the current flow because its threshold voltage was higher than 0 V. The entire block is marked as bad block by the memory controller and no longer addressed [2].

The retention concept instead, is the ability of a memory to keep a stored information over time with no biases applied. Electron after electron, charge loss could slowly leading up to a read failure: a programmed cell can be read as erased if its VT shifts below 0 V. The intrinsic retention is mainly limited by tunneling (see Fig.1.5) through the oxide even if thermionic emission mechanisms over the barrier can be considered. Recent studies [6] demonstrated that an oxide thickness of 4.5 nm is enough for granting theoretical intrinsic retention of 10 years, which is the minimum limit imposed by present standards. The cell retention worsen with

Figure 1.3: Band diagram during a program operation: without traps (solid lines in the oxide region) and with traps (dashed lines in the oxide regions).

Figure 1.4: Threshold voltage degradation during cycling of NAND Flash with different geometrical features.

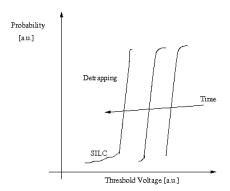

memory cycling and this effect is appreciable as a reduction of the VT levels as sketched in Fig.1.6 showing the time evolution of the cumulative VT distribution of programmed cells. Charge loss from the floating gate moves the VT distribu-

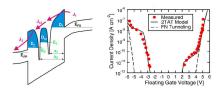

tion towards lower values. In additions, a tail in the lower part of the distribution indicates that a small percentage of cells is losing charge faster than average. The rigid shift of the cumulative VT distribution can be related to the oxide degradation within the oxide and at the Si - SiO<sub>2</sub> interface. As described early, successive electron tunneling leads intrinsically to oxide degradation, characterized by traps generation. These traps may be responsible for charge loss from the floating gate towards the silicon substrate. In fact, an empty trap suitably positioned within the oxide can activate trap assisted tunneling (TAT) mechanisms characterized by a significantly higher tunnel probability with respect to a triangular barrier unmodified by the trap presence. In addition, an electron trapped within the oxide during writing operations and responsible for the VT increase leading up to endurance failures may be detrapped when the program pulse is switched off, when the cell is read or even when the cell is not addressed. As a result, the empty trap may enhance the TAT phenomenon (assuming a positive charged trap) and, in addition, it can increase the electron field at the Floating gate-tunneling oxide interface thus raising the electron tunnel probability. The required activation energy for detrapping has been calculated in several experiments about 1.1 eV [7]. It is clear that these mechanisms are strongly related to the oxide degradation and therefore data retention decreases with the number of applied writing pulses. Results of retention stresses showed that the cells contributing to the tails of the VT distribution are characterized by a leakage current larger than the average at the same stress level [8]. The Stress Induced Leakage Current (SILC) of these cells is attributed to TAT process of carriers through the tunnel oxide traps. By modeling the behavior of the tail cells it has been shown that a single TAT model is not consistent with the observed leakage current. The charge loss of these cells is attributed to a tunneling process assisted by two traps (2TAT) - see Fig. 1.7. The characteristics of this phenomenon are the opposite with respect to detrapping: low activation energy (0.1 - 0.3 eV) and strong field acceleration. SILC affects a larger number of cells after each writing cycle, thus confirming that also this abnormal charge loss is driven by oxide degradation. The position of leaky cells within the array, however, does not show any clusterization which could be related to a technological process. In addition, the abnormal leakage is not permanent: a cell can exhibit a SILC effect after a cycle and behave as normal when erased and reprogrammed. This result is consistent with a model requiring 2 traps with suitable locations within the oxide to activate a SILC effect. Some of these cells can suffer an erratic behavior [9] due to a trap annihilation/reactivation process. It has been proved, however, that traps are annealed over 85C so high temperatures partially mitigate this effect [10].

Figure 1.5: Band diagram of the cell when programmed and not biased. The main mechanism for data loss is tunneling through the tunnel oxide.

Figure 1.6: Cumulative distribution of a NAND array on Program state. Both detrapping and SILC effects are appreciable on the time evolution.

Figure 1.7: Two traps assisted tunneling (2TAT) band diagram (left) and comparison between the SILC-2TAT model result versus the classical Fowler-Nordheim theory (right).

#### 1.2 Emerging issues of Flash technology

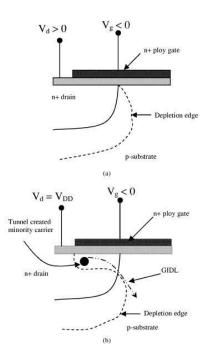

As the technology scaling of Flash proceeds, emerging reliability threats have to be considered in addition to the traditional issues presented in the previous sections. The influence of phenomena like the Gate-Induced Drain Leakage and the injection statistics cannot be neglected during the validation phase of a technology since they introduce new disturb types during the common operations of a module.

The Gate Induced Drain Leakage (GIDL) is a major leakage mechanism occurring in OFF MOS transistors when high voltages are applied to the Drain and it is attributed to tunneling taking place in the deep-depleted or even inverted region underneath the gate oxide [11]. When the gate is biased to form an accumulation layer at the Silicon surface, the surface behave like a p region more heavily doped than the substrate. This effect causes the depletion layer of the junction at the surface to be more narrow than elsewhere. The narrowing of the depletion layer near the surface increases the local electric field thus enhancing high field effects near that region. When the gate voltage in a nMOS transistor is 0 V (or below) and the Drain is biased at a high voltage, the n+ drain region under the gate can be depleted or even inverted (see Fig.1.8). This effect causes a peak field increase leading up to high field phenomena such as avalanche multiplication and band-toband tunneling. The band-to-band tunneling probability can also be increased by the presence of surface traps, resulting in a band-trap-band tunneling. As a result of these effects, minority carrier are emitted in the drain region underneath the gate and swept laterally to the substrate which is at a lower potential, thus completing a path for the leakage current. Fig.1.9 shows the sub-threshold characteristics in an nMOS transistor for different Drain voltages [12]. On NAND arrays the GIDL has been found to produce erroneous programming in specific cells, that is those belonging to WLO, adjacent to the SSL transistor. The SSL transistor is OFF during programming and GIDL effects may be present if its drain is driven at high voltages. This situation occurs because of the self-boosting techniques adopted to prevent programming. As shown in Fig.1.10, if WL0 is driven at Vpgm to program the cell in the central column, the channel voltage of the cells sharing the WL0 line are to be raised to prevent their programming. Because of the selfboosting technique, the source terminal of those cells (therefore also the drain node of their adjacent SSL transistors) are raised to values higher than VCC, thus leading up to bias configurations activating GIDL effects. The electron-holes pair generation follows and the generated electrons are accelerated at the SSL - WL0

space region and can be injected as hot electrons in the floating gate of WL0 cells. Also the DSL transistors may trigger GIDL mechanims when boosting effects take place on cells sharing WL31, but since the voltage applied to the DSL gate line is VCC, the consequences suffered by cells belonging to WL31 are much lower with respect to those sharing WLO. Fig.1.11 shows experimental data for 3 different cells: WL0 and WL31, potentially affected by GIDL disturbs, and a reference one located in the middle of the string. This unwanted programming in specific cells is supposed to burden in scaled architectures, since a reduced separation between WL0 and SSL lines will increase the accelerating fields for hot electrons. Recently, to mitigate GIDL effects, it has been proposed to introduce two dummy world lines to separate the two select transistors and the effective string of cells. To reduce the impact of these two additional word lines, longer strings of 64 cells have been proposed to improve area efficiency. A higher number of cells in series (64 cells vs 32 of standard architectures), however, increase the string resistance so that word-line voltage modulation are required during read and programming thus ensuring that proper voltage levels are applied depending on the cell location within the string. For instance, a higher word-line voltage is used when accessing a cell near the top of the string (close to the bit line) to compensate for the string resistance.

The aggressive scaling of Flash memories, necessary to improve their performances, brings attention also to the discrete nature of the charge stored in the floating gate. The number of electrons determining the stored information, in fact, continuously decreases with the tunneling area dimension. When only few electrons control the cell state (i.e. setting the transistor threshold voltage), their statistical fluctuations determine a non-negligible spread. These fluctuations may

Figure 1.8: Condition for the depletion region near the gate-drain overlap region of a nMOS transistor when the surface is accumulated with a low negative gate bias (a), and n+ region is depleted or inverted with high negative gate bias (b).

Figure 1.9: Leakage current measured in a nMOS transistor for different Drain-Source voltages VDS in the subthreshold regime. When VGS approaches 0 V, for high VDS values the leakage current is due to GIDL.

be attributed to the statistics ruling the electron injection into the floating gate during program or to the electron emission from the floating gate during erase or retention, both related to the granular nature of the current flow [13]. A slight variation of the number of electrons injected during programming may produce VT

Figure 1.10: Bias conditions possibly activating GIDL effects on SSL transistors belonging to columns  $BL_{i-1}$  and  $BL_{i+1}$ .

Figure 1.11: Measured program disturbs characteristics for 3 cells belonging to WL0, WL15 and WL31, respectively. NOP indicates the number of partial programming when multiple writing of a world line is allowed for specific applications. It can be observed that, for higher values of Vpass, the disturb on cell WL0 becomes significant.

variations possibly leading to errors in MLC architectures. Cells in NAND MLC architectures are programmed by using a staircase voltage on the control gate.

This kind of waveform allows achieving a constant current Fowler-Nordheim tunneling: by increasing the wordline voltage after each short pulse it is possible to compensate the field reduction that follows the electrons injection into the floating gate (see Fig.1.12). For sufficiently large step numbers, a linear VT increase is obtained, with a  $\Delta VT$  per step almost equal to the applied voltage step but leading to a significant VT distribution enlargement (see Fig.1.13). This is due to the programming current convergence toward an equilibrium stationary value, corresponding to an average number of electrons transferred to and from the floating gate for each step [14]. The discrete nature of the charge flow introduces, for each cell, a statistical spread contribution to the resulting VT after each step. It has been evidenced that the threshold voltage variation spread, indicated as  $\sigma_{\Delta VT}$ , depends only on the parameter Vstep of the programming waveform (i.e. on the injected charge per step qn) and not on the pulse duration and on the number of pulses to achieve  $\Delta VT$ .

Figure 1.12: Electrostatic effect on the injection process: the Floating Gate (FG) potential changes when an electron is injected from the substrate (a) to the FG (b), reducing the tunnel oxide field and the tunneling current.

Figure 1.13: Probability distributions of the injection statistics with and without the contribution of the RTN (Random Telegraph Noise).

## Chapter 2

# **Phase Change Memories**

Phase Change Memory (PCM) is one of the most promising emerging Non-Volatile Memory (NVM) technology thanks to fast writing operations, long endurance and very good radiation hardness. PCMs offer direct write (any bit can be independently reprogrammed with no need for block erasing), improved write throughput versus NOR-based memories and random access time versus NAND-based memories, as well as the potential to be scalable beyond Flash technology [15]. Moreover, PCMs ensure high endurance and good compatibility with standard CMOS fabrication processes. Although a relevant effort is still being put on design optimization and material analysis, the PCM technology has today reached a significant level of maturity so that test chips containing multimegabit arrays of cells are commonly available for electrical characterization purposes. As a result, a significant amount of statistical information can be provided to the reliability/cell design engineer.

#### 2.1 Physics of chalcogenide-based memories

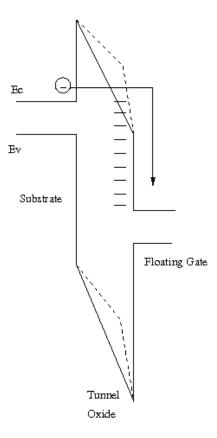

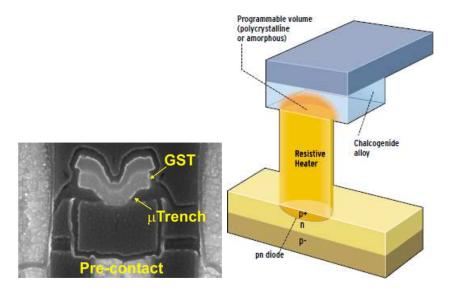

In PCMs, the storage device is made of a thin film of chalcogenide alloy (in our case, Ge2Sb2Te5, GST) [16]. This material can reversibly change between an amorphous (high impedance, RESET state) and a polycrystalline (low impedance, SET state) phase when thermally stimulated via Joule heating, thus allowing information storage. The phase conversion of a storage element is obtained by appropriately heating (by means of electrical pulses applied to a suitable heater element) and then cooling a small, thermally isolated portion of the chalcogenide material. Fig. 2.1 shows a cross section of a PCM cell and its relative graphic representation. Once the chalcogenide material melts, it completely loses its crystalline structure. When rapidly cooled, the chalcogenide material is locked into its amorphous state (to this end, the cooling operation rate has to be faster than the crystal growth rate). To switch the memory element back to its crystalline state, the chalcogenide material is heated to a temperature between its glass transition temperature and its melting point temperature [17]. In this way, nucleation and micro-crystal growth occur in tens of nanoseconds, thus leading to a (poly)crystalline state. From above, it is apparent that the storage element can be modeled as a programmable resistor (high resistance = logic 0; low resistance = logic 1). Reading a cell basically consists in measuring the resistance of the addressed storage device. To this purpose, a predetermined voltage is forced across the storage element of the selected cell, and the resulting current flow is sensed.

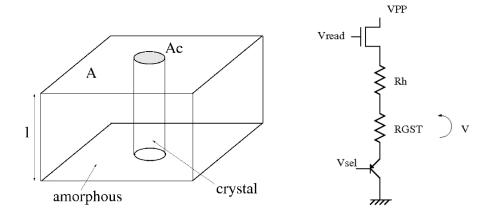

Figure 2.1: Cross section of a PCM cell (left) and its relative graphic representation (right).

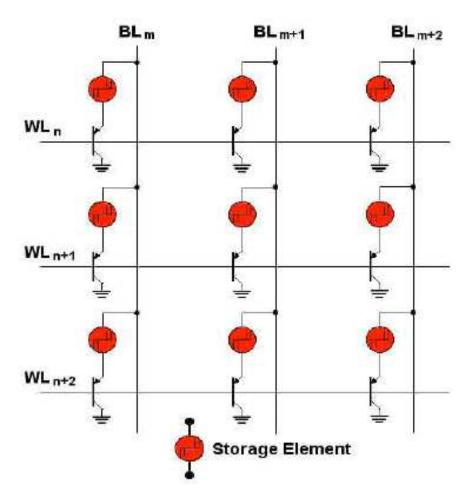

#### 2.2 Electrical characterization of PCM arrays

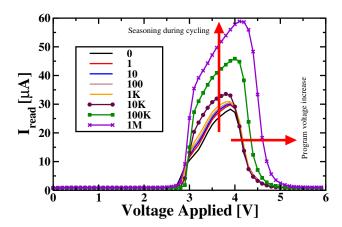

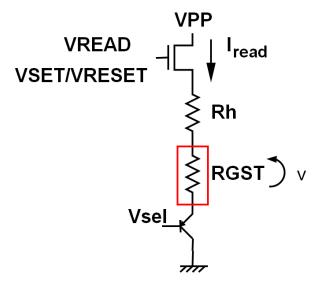

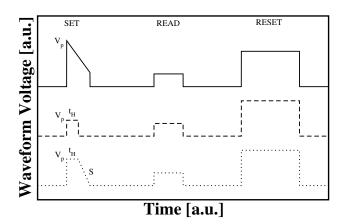

All characterization measurements have been performed on a 512 Kbit population of PCM cells with the aid of a dedicated testing equipment. Fig. 2.2 depicts a detail of the memory cell integrated in an array environment. A pnp Bipolar Junction Transistor (BJT) is employed as the cell selector in order to minimize silicon area occupation, and, hence, improve data storage density. Read voltages and write voltages are transferred to the cells through a select nMOS transistor supplied by  $V_{pp} = 4.8V$ . A heater resistance  $R_h$  is in series with  $R_{GST}$ , representing the resistance of the GST active element. Details on the 180 nm PCM technology characterized in this thesis can be found in [18]. The read current of the cell can be measured in a Direct Memory Access mode by applying a read voltage at the control gate of the select nMOS transistor. The SET and RESET operations are performed similarly by applying a SET/RESET pulse at the control

Figure 2.2: Typical PCM array topology with pnp bipolar transistors as a selecting element.

gate of the select nMOS transistor.

A set of Relevant Electrical Parameters (REP) has been defined and characterized on test chip arrays [19]:  $V_{th}$ ,  $V_{T1}$ ,  $V_{T2}$ ,  $V_{s}$ ,  $I_{max}$ , and  $R_{set}$ . REP are intended to provide a synthesis of results obtained from key characterization procedures which are commonly adopted on single cell study. The synthesis becomes important when the same procedures are applied to a population of cells. The dynamic I-V characteristics describe both the SET curve and the RESET curve which

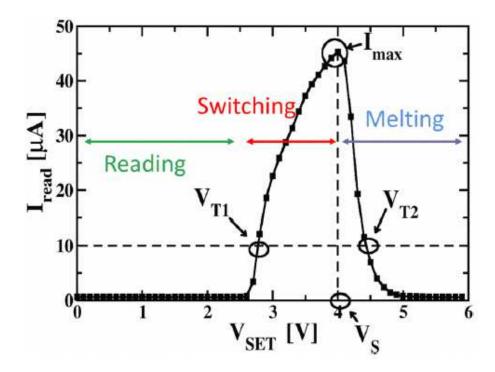

are measured by applying the sequence of pulses shown in Fig. 2.3a-b. Fig. 2.4 shows the I-V curves obtained by averaging the I-V curves of all the cells of the array. These curves can be described in terms of at least two parameters which can be easily extracted from the data:  $R_{set}$  and  $V_{th}$ . When a complete IV characterization is performed for each cell of a 5I2K population, 80MB of data are collected, whereas the extraction of REP allows a more easy analysis on 4MB of synthetic data only. The R-I curve describes the read current (or equivalently the resistance) as a function of the SET pulse amplitude. The R-I curve is measured by applying the sequence of pulses shown in Fig. 2.3c. Fig. 2.5 shows the R-I curve obtained by averaging the R-I curves of all the cells of the array. These curves can be described in terms of four parameters which can be easily extracted from the data:  $V_{T1}$ ,  $V_{T2}$ ,  $V_s$ ,  $I_{max}$ .

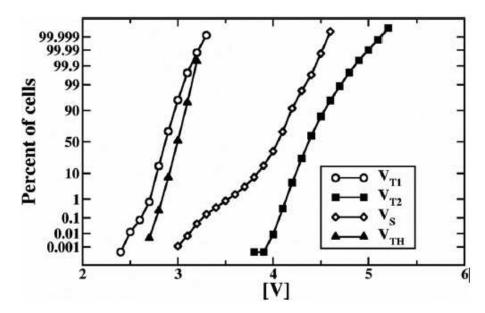

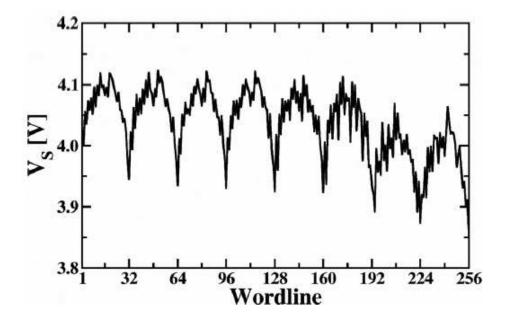

When a complete R-I characterization is performed for each cell of a 512 Kb population, 60MB of data are collected, whereas the extraction of REP allows a more easy analysis on 8MB of synthetic data only. The usage of synthetic parameters allows the analysis of statistical behavior of a cell population as shown in Fig. 2.6. From these graphs it is possible to evidence some anomalous behavior like, for example, the one shown in the  $V_s$  distribution which exhibits a tail at its lower left corner. A further analysis of  $V_s$  over the whole cell population allows to show that this feature is related to the array architecture and in particular to the cell distance from the bitline strap contact (see Fig. 2.7). Standard reliability cycling tests can be performed and results effectively displayed by using REP. Fig. 2.8 shows the behavior of the cell population displaying the average values of  $V_{th}$ ,  $V_{T1}$ ,  $V_{T2}$  and  $V_s$  during a 1M SET/RESET cycle experiment. This figure summarizes significant results. The switching threshold value decreases during

Figure 2.3: Waveforms applied to each cell in the array to perform the dynamic I - V characterization and the extraction of  $R_{set}$  and  $V_{th}$ .

cycling although only after some hundred thousands cycles. This phenomenon has to be taken into account in the design of the reading voltage. There is also an increase of  $V_{T2}$  which can interfere with the RESET operation. Fig. 2.9 shows the increase of the maximum current of the R-I curve and the decrease of the SET resistance with cycling. This result clearly indicates that cells undergo a better crystallization with cycles, a phenomenon sometimes called cell seasoning.

## 2.3 Optimization of the writing operations

Different voltage waveforms are used for both programming (or RESET) and erasing (or SET) operations in PCM, referring to the GST amorphization and crystallization processes, respectively. The main differences consist on the voltage, the

Figure 2.4: Result of the dynamic I-V characterization. The two curves on display are the average over the whole cell population.

length, and the shape of the applied waveforms. Typically, the programming operation is achieved by using a voltage pulse, bringing the GST above its characteristic melting point, then cutting away the pulse rapidly, in order to melt and then amorphize the GST. The erasing operation, instead, can be achieved in many ways, due to multiple possibilities for achieving crystallization of active chalcogenide. Many reliability issues of multimegabit memory arrays have been tackled in the last few years, mainly concerning the used phase change materials and the cell geometrical parameters. However, a detailed analysis of the impact of waveform parameters on the overall reliability of large arrays is still missing, in particular for the erasing case where the randomness of the crystal nucleation physics in chalcogenide materials plays a basic role [17].

The waveform applied to erase a PCM cell has the objective to create linked

Figure 2.5: R-I characterization. The curve on display represents the average over the whole cell population.

Figure 2.6: Distribution of  $V_{T1}$ ,  $V_{T2}$ ,  $V_s$ , parameters in a Gaussian probability plot.

Figure 2.7: Average value of  $V_s$  versus the wordline index. Each point is the average over the columns belonging to the considered wordline.

Figure 2.8: Average values of  $V_{th}$ ,  $V_{T1}$ ,  $V_{T2}$  and  $V_s$  during cycling.

Figure 2.9: Average values of  $I_{max}$ , and  $R_{set}$  during cycling.

crystal grains inside the programmable region (PR) and then ensure a low resistivity path between the cell polycrystalline GST and the heater. Crystal grain creation follows a nucleation dynamic [17], taking place pseudo-randomly inside the whole active area, following the electrical field distribution generated by the voltage waveform.

To compare and optimize erasing waveforms some comparison criteria are to be introduced:

- Number of waveform parameters. Each waveform has a typical set of parameters that can be varied in order to achieve the desired erasing target.

Having more parameters, a greater complexity is introduced during the waveform analysis.

- Array current mean value  $\mu$  [ $\mu$ A]. This parameter is a target for erase operation. It mainly represents the endpoint of the crystallization process.

• Array current standard deviation  $\sigma$  [ $\mu A$ ]. The distribution of the cells read currents after erase,  $I_{cell}$ , is found to follow a gaussian behavior. The standard deviation  $\sigma$  is an indicator of how the erasing algorithm is able to keep the distribution compact.

There are three common approaches for achieving erasing operation:

- Melt and crystallize: the formation of the low resistive path is preceded by a melting operation in the PR.

- Crystallize once: the phase transition from amorphous to crystal is achieved by applying to the cell a voltage below the melting point  $V_m$

- Burst crystallization: the grain nucleation is achieved by a sequence of short voltage pulses applied to PR.

Each method requires suitable waveforms. Optimization is achieved by following the flow represented in Fig.2.11.

Melt and Crystallize Waveform (MCW) belongs to the melt and crystallize approach. It is constituted by two parts: the former is a linear drop from a peak voltage  $V_p$  higher than  $V_m$  to 2 Volts; the latter is a rapid ( $\approx$  10 ns) voltage cut to 0 V (see Figs.2.10a). The initial part of the waveform must provide a sufficient heat inside PR, driving it to melt. Once the GST is completely molten the successive crystallization process starts from a fully amorphized material where precrystallized spots within PR have been certainly removed. Crystallization starts when the waveform is above  $V_m$  and ends slightly above 2 Volts, so that the grain formation and the percolation path creation is a slow process. MCW allows getting low  $\sigma$  values (thus compact distributions), but it is difficult to control the  $\mu$

value. MCW is also called a *one parameter waveform*, since only  $V_p$  can be optimized. As can be seen in Fig.2.12, by lowering this parameter the  $I_{cell}$  distribution broadens significantly and a large tail for low  $I_{cell}$  values is observed. This is related to the erasing approach followed by MCW: if  $V_p$  is not sufficiently larger than  $V_m$  the crystallization process does not necessarily starts from a fully molten material and the subsequent dynamics can vary from cell to cell. A too large  $V_p$ , however, may overstress the GST structure due to the melting process. Since MCW may produce the tightest distribution with respect to the other waveforms, the limitation of  $\sigma$  can be the optimization goal. Therefore  $V_p$  could be increased until the required  $\sigma$  has been reached. Fig.2.13a and Fig.2.13b confirm the poor ability to control the crystallization dynamic, showing the rapid saturation of  $\mu$  and  $\sigma$  values.

Sloped Crystallize Once Waveform (SCOW) is used for a crystallize once approach. Its shape is that of a rectangular trapezium, with  $V_p < V_m$  (see Figs.2.10b). The crystallization process starts from the previous amorphous state. After a hold time  $t_H$ , in which the voltage is kept at  $V_p$ , the voltage is linearly driven to 0, waiting for the complete crystal grains formation. The controlled parameters are:  $V_p$ , that influences the crystal grains formation speed,  $t_H$ , the time  $t_s$  required to reach 0 V, which also define the slope (S) parameter as  $S = V_p/t_s$ . The availability of 3 adjustable parameters makes SCOW also suitable for multilevel applications, since the average current value can be controlled while keeping a tight distribution. Since  $V_p$  is mandatory for knowledge of crystallization speed, is therefore requested a determination of its optimum value, thus granting an acceptable trade-off between compactness of  $I_{cell}$  and higher read window margin. As shown in Fig.2.14, by applying  $V_p$  closer to  $V_m$ ,  $I_{cell}$  exploits large tails into

distribution, due to unwanted melting, that can occur in cells characterized by a  $V_m$  value lower than the expected for the array. Same tails appears when  $V_p$  is not sufficiently larger to grant correct crystallization. The best solution evaluated, that will be furthermore used for BCW and COW, is  $V_p = 3.75$  V.  $t_H$  has been found to affect only the  $\mu$  parameter, so that it can be conveniently adjusted to shift the entire  $I_{cell}$  distribution in multilevel application. The slope S, on the contrary, influences also the  $\sigma$  parameter and therefore it must be optimized in order to tighten the  $I_{cell}$  distribution. Fig.2.15a and Fig.2.15b show the  $\mu$  and  $\sigma$  dependency on S. An optimized value S=1 is found.

Crystallize Once Waveform (COW) and Burst Crystallize Waveform (BCW) are used for a *crystallize once* approach and are characterized by a rectangular shape (see Figs.2.10b). With respect to SCOW the crystallization process ends abruptly. The key parameter is  $t_H$ , that allows controlling the average read current after erase, making COW also suitable for Multi-levels architectures. A too short  $t_H$  may otherwise provoke parasitic programming phenomena, especially if

$$t_H \le t_d \tag{2.1}$$

where  $t_d$  is the characteristic delay requested by PR to create the percolation path. It has been decided to group the COW and the BCW optimization, due the evident similarity of the waveforms. The main difference consists in the presence of the R parameter on the BCW, which allows to implement the burst crystallization process using the crystallize-once mechanism as base. The COW waveform is characterized by two parameters:  $V_p$  and  $t_H$ . BCW can replace COW when a deeper control on parasitic programming phenomena (such as verify algorithms on Flash

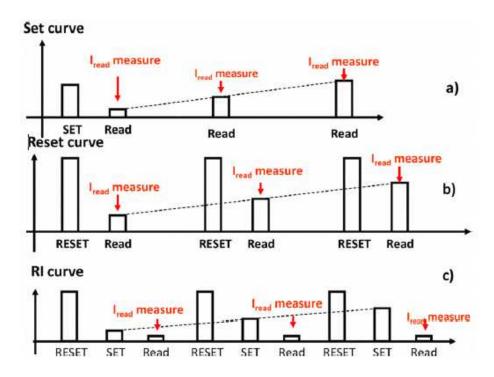

memories) is required in multi levels architectures (see Figs.2.10a). This waveform realizes the burst crystallization approach and it is constituted by a sequence of short box pulses. The physical mechanism behind the crystal grains formation is a slight variation of that achieved by COW, since the pulse is removed before the complete grain formation. A burst of COWs is applied, thus creating a sort of temperature elastic effect, in which the temperature rise (well below the melting point) increases the crystallization process speed, while the temperature fall induces a stabilization of the grain size. The three BCW characteristic parameters are:  $V_p$ , the pulse duration  $t_H$  and the repetition number R of the standard pulse. The first two parameters are the same of COW, so that they influence the  $I_{cell}$  in a similar way. The last parameter is only used to reach longer exposure times. Critical issues related to the use of BCW may arise if (2.1) is not respected or if the typical RC delays of the chip circuitry are not correctly taken into account, which may force crystal grains to be reabsorbed into amorphous structure. It has been first analyzed the dependance on  $V_p$  with the same methodology used for SCOW, finding an optimal value of 3.75 V, resulting in the lowest  $\sigma$  and in the smallest  $I_{cell}$  distribution tail (see Fig.2.14). As for  $t_H$ , a strong dependance has been found for both  $\mu$  and  $\sigma$  criteria, only for very short times (see Fig.2.16a and Fig.2.16b). This result can be explained by the nucleation dynamics: the final  $I_{cell}$ value saturates after the end of the crystal grains growth phase [19] (occuring, in this study case, after  $\simeq 500$  ns).

The performed study can be further extended to non-common erasing waveforms such as full exponential (ECOW) and ramped exponential (RECOW). Table 2.1, resume the details of the analyzed waveforms.